从事PCB设计工作,通过兼职接取订单可以赚取更多收入,同时也能增强自身技能。接下来,我将从多个角度为大家详细介绍PCB设计兼职接单的关键点。

提升设计能力

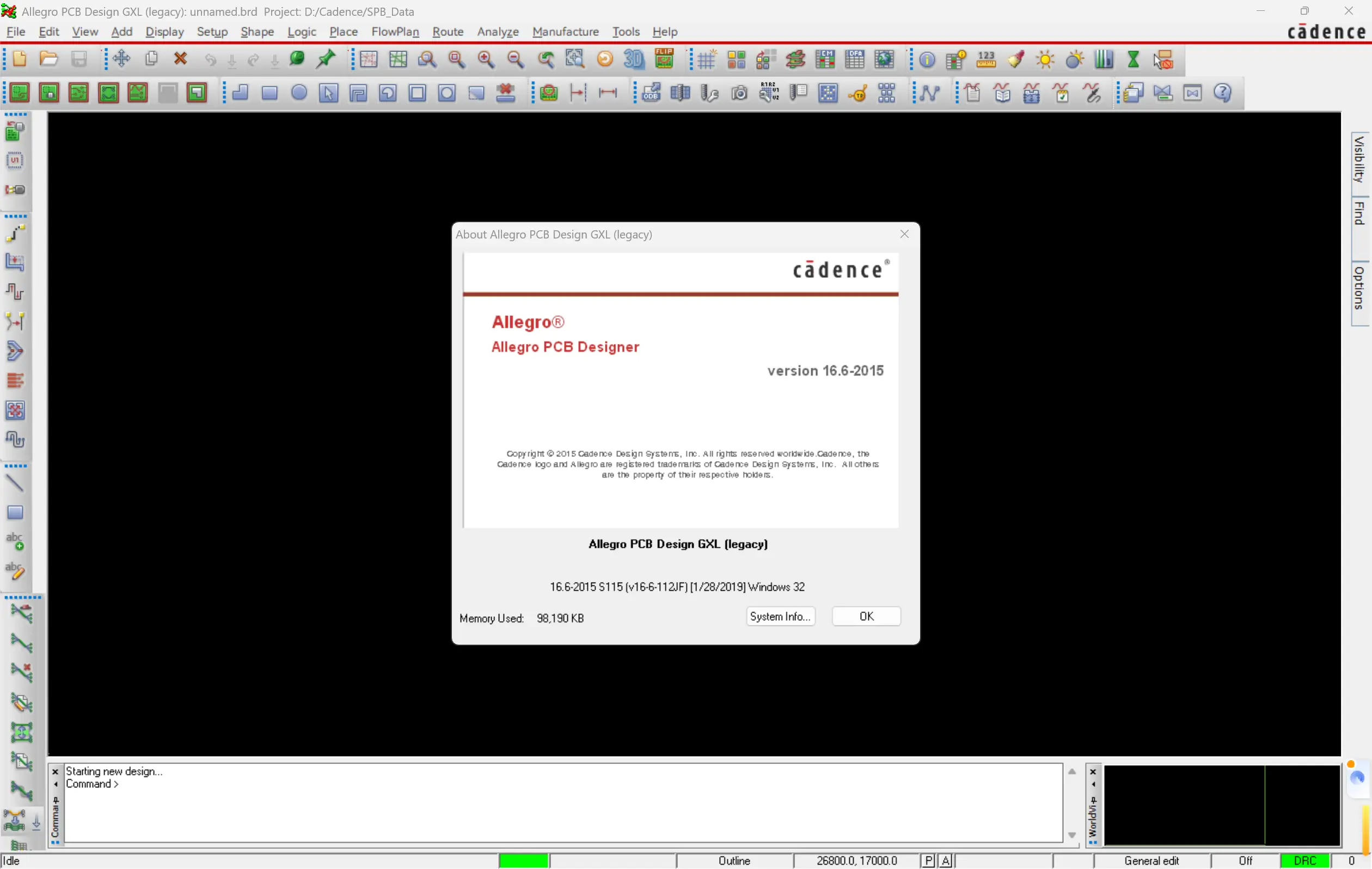

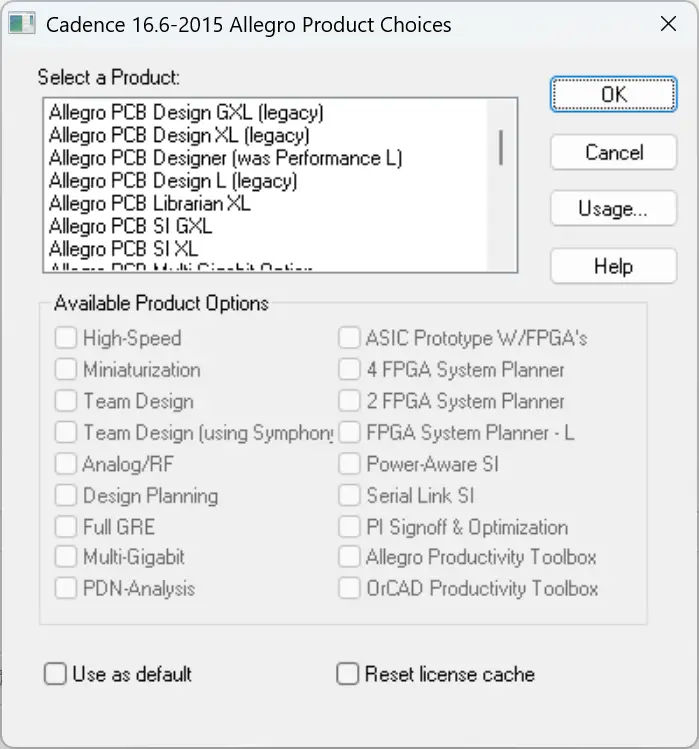

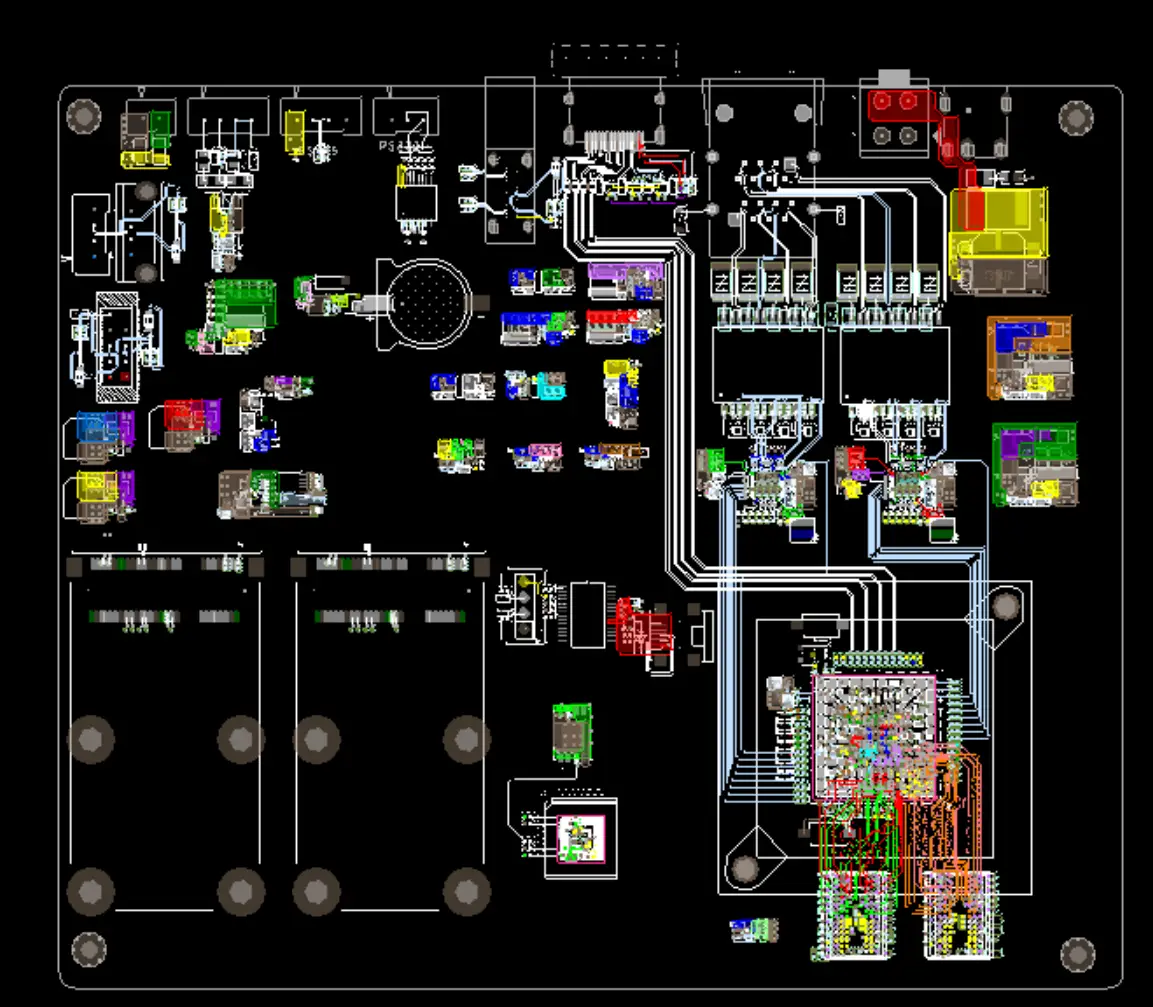

进行PCB设计,若技术不够精湛,接单会变得困难。平日里,需认真掌握PCB设计软件的使用方法,比如Altium Designer等工具的操作。同时,还需广泛研究各类PCB设计案例,涵盖消费电子、工业控制等多个领域,以此不断提高个人设计水平。

积攒项目经验

项目经验丰富,接兼职任务自然更轻松。可以先从小处着手,比如协助同学完成毕业设计,或是帮助小型企业解决简单的PCB设计难题。每个项目完成后,及时总结心得,积累各类PCB设计的经验,这样在遇到复杂订单时也能应对自如。

拓展接单渠道

需多途径寻求接单机会。首先,在专业兼职平台注册,上传个人资料,积极寻找订单。其次,加入PCB设计领域的交流群,活跃参与讨论,偶尔也能遇到兼职信息。

合理定价收费

在确定价格时,需全面考虑各种要素。可以参照同类设计在市场上的价格水平,依据设计的复杂程度和时间投入来制定合理的价格。避免无谓的低价竞争,同时也要注意避免定价过高导致客户流失。初期可以采取较低的价格承接一些小项目,积累良好口碑后,再逐步调整价格。

维护客户关系

客户关系的维护至关重要。设计任务完成后,应迅速与客户取得联系,听取他们的意见。若客户有修改要求,应予以细心调整。与客户维持顺畅的交流,力求获得后续的持续合作,如此一来,兼职订单数量有望持续增加。

各位朋友,在进行PCB设计兼职接单时,你们有没有遇到过什么棘手的问题?欢迎在评论区留言讨论。觉得这篇文章对您有帮助,不妨点个赞,并分享给更多人。