RS-485 概述

RS-485 和 RS-232 一样,都是串行通信标准,现在的标准名称是 TIA485/EIA-485-A ,但是人们会习惯称为 RS-485 标准, RS-485 常用在工业、自动化、汽车和建筑物管理等领域。

RS-485 总线弥补了 RS-232 通信距离短,速率低的缺点, RS-485 的速率可高达 10Mbit/s ,理论通讯距离可达 1200 米; RS-485 和 RS-232 的单端传输不一样,是 差分传输 ,使用一对双绞线,其中一根线定义为 A ,另一个定义为 B 。

双绞线

▉ RS-485 物理层

RS-485 的物理层负责在设备和物理传输介质之间传输原始数据。它处理电信号到数字数据的转换,同时定义电压、时序、数据速率等。

① 差分信号

长距离布线会有信号衰减,而且引入噪声和干扰的可能性更大,在线缆 A 和 B 上的表现就是电压幅度的变化,但是,采用 差分 线 的好处就是,差值相减就会忽略掉干扰依旧能输出正常的信号,把这种差分接收器忽略两条信号线上相同电压的能力称为 共模抑制 。

标准规定了,逻辑 1 : +2V to +6V ;逻辑 0 : -6V to -2V 。

RS-485 不需要使用特定的总线电压,只看最小差分电压,在较长的电缆长度上,接收器接收到的电压可能会降低到 +/- 200 mV ,这对于 RS-485 仍然是完全可以接受的,这也是 RS-485 的优点之一。

很多收发器的标准达到甚至超过 TIA/EIA-485A 规范,在实际使用中,以器件的 SPEC 参数为主,如下某收发器的负输入阈值最小也是 -200mV 。

② 信号定义

现在很多的 RS-485 转换器都是兼容 RS-422 的,所以看到很多转换器上面的信号都是 T/R+ 、 T/R- ,即对应 RS-485 的 A+ 和 B- 。

对于 DB9 针型的母头, RS-485 有如下的接线定义示意, Pin6~Pin9 为 N/A 不接。

DB9

输出信号

RS-422全双工接线

RS-485半双工接线

1

T/R+

发(A+)

RS-485(A+)

2

T/R-

发(B-)

RS-485(B-)

3

RXD+

收(A+)

空

4

RXD-

收(B-)

空

5

GND

地线

地线

③ 拓扑结构

RS485 有两线制和四线制两种接线,四线制只能实现点对点的通信方式,现很少采用,多采用的是两线制接线方式,这种接线方式为总线拓扑结构,在同一总线上最多可以挂接 32 个节点。

RS-485 总线同 I2C ,也是主从模式,支持点对点单从机模式,也支持多从机模式,不支持多主机模式。

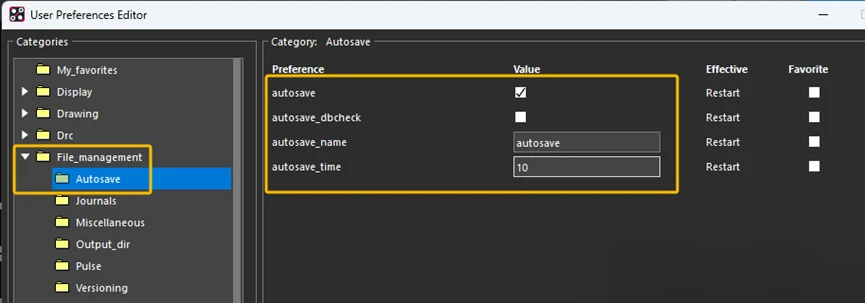

▉ RS-485 收发器

RS-485 是差分传输,如果用单片机控制 RS-485 接口的设备,需要用到 收发器 ,这一点和 CAN 总线是类似的,如下是一个 MCU 控制一个 RS-485 的图示。

收发器内部是一个接收器(上半部分)加一个发送器(下半部分),下面简单说说收发器的原理,便于理解 MCU 是如何和 485 设备通信的。

RS-485 收发器内部结构

其中:

A 和 B 为总线;

R 为接收器输入;

RE 为接收器使能信号;

DE 为发送器使能信号;

D 为发送器输出;

对于使能信号,字母上面加一横的为低电平有效(如上图 RE ),不加的为高电平有效(如 DE )。

对于发送器,有如下的真值表:

1 、当驱动器使能引脚 DE 为逻辑高时,差分输出 A 和 B 遵循数据输入 D 处的逻辑状态。 D 处的逻辑高导致 A 转为高, B 转为低。在这种情况下,定义为 VOD=VA-VB 的差分输出电压为正。当 D 为低时,输出状态反转, B 变高, A 变低, VOD 为负。

2 、当 DE 低时,两个输出都变成高阻抗。在这种情况下,与 D 处的逻辑状态是不相关的。

发送器真值表

对于接收器,有如下的真值表:

1 、当接收器使能引脚 RE 逻辑低时,接收器被激活。当定义为 VID=VA–VB 的差分输入电压为正且高于正输入阈值 VIT+ 时,接收机输出 R 变高。当 VID 为负且低于负输入阈值 VIT- ,接收机输出 R 变低。如果 VID 在 VIT+ 和 VIT- 之间,则输出不确定。

2 、当 RE 为逻辑高或悬空时,接收机输出为高阻抗, VID 的大小和极性无关。

接收器真值表

▉ RS-485 数据链路

上面讲到的 RS-485 收发器的工作原理,下面简单描述 RS-485 的数据链路,可以先看一下通俗易懂的 UART 协议帧格式

主机发送给从机或者从机发送给主机,都会占用到 A 和 B 线,所以 RS-485 多用在半双工模式。

主机的 GPIO 会控制 RS-485 收发器的 DE 管脚,设置发送模式,从 UART TXD 线向 RS-485 收发器的数据( D 或 DI )线发送一个字节,收发器将在 A 和 B 线上将单端 UART 位流转换为差分位流,数据离开收发器后,主机立即将收发器的模式切换为接收模式。

从机和主机是类似的,从 机控制 RS-485 收发器的 /RE 管脚,设置为接收模式,接收主机发送的比特流,将其转换为单端信号,通过从机的 UART RXD 线接收,当从机准备好响应时,它按主机原来的方式进行发送,而主机变为接收。

▉ RS-232 和 RS-485 转换

RS-232 和 RS-485 之间可以转换,一个方法是 RS-232 转换成 TTL ,再由 TTL 转换为 RS-485 ,当然也有芯片支持将 RS-232 直接转换成 RS-485 ,网上有很多模块。

RS-232 和 RS-485 转换模块

▉ RS-485 和 CAN 的区别

虽说 RS-485 没有标准的数据协议格式,但和 CAN 总线在很多地方是有相似的,比如 A&B 和 CANH&CANL 都是差分信号,通信都需要收发器,都需要 120 欧姆的匹配电阻等等。

总线特性

CAN总线

RS-485总线

硬件成本

稍高

低廉

总线利用率

优先级自动仲裁,利用率高

采用轮询,利用率低

数据传输率

高

低

错误检测机制

控制器带校验机制,保证底层数据传输正确

只有物理层规范,无数据链路层规定

单节点故障影响

总线无影响

总线瘫痪

开发成本

软件开发灵活,时间成本低

开发难度较大

系统成本

较低

高

▉ RS-485 常用电路

网上找的一个常用的 RS-485 电路,其中需要注意两点:

1 、使能信号 RE 和 DE 可采用一个 GPIO 控制,节省资源, GPIO25 输出高电平, RE=DE=0V ,进入接收模式; GPIO25 输出低 电平, RE=DE=3.3V ,进入发送模式。

2 、有一些电路中会在 A 上加上拉, B 上加下拉电阻,主要原因是: RS-485 总线在 idle 状态,电平是不固定的,即电平在 -200mV~+200mV 之间,收发器可能输出高也可能输出低, UART 在空闲时需要保持高电平的,如果此时收发器输出一个低电平,对 UART 来说是一个 start bit ,会导致通信异常,关于 Ru 和 Rd 的阻值在这里不作过多赘述,后面有机会 会 详细写一篇文章。

关于第二点,需要注意:

① A 上加上拉, B 上加下拉,接反数据通信也可能出错。

② 某些收发器内部集成上下拉电阻,则外部不需要再添加。