一、资料简介

各位硬件工程师、嵌入式开发者、电子爱好者,大家好!

智行者 IC 社区为大家整理了348 个经典实用电路图,覆盖电源、音频、传感器、通信、控制等多个领域,全部为可直接参考的 PDF 原理图,从入门级小电路到工业级设计方案都有收录,是电子设计路上的高效速查工具包。

这份资料里没有复杂的理论堆砌,只保留可落地、可复用的电路实现,不管是课程设计、项目开发还是日常调试,都能快速找到参考方案,帮你节省大量查资料、画原理图的时间。

二、核心分类与亮点

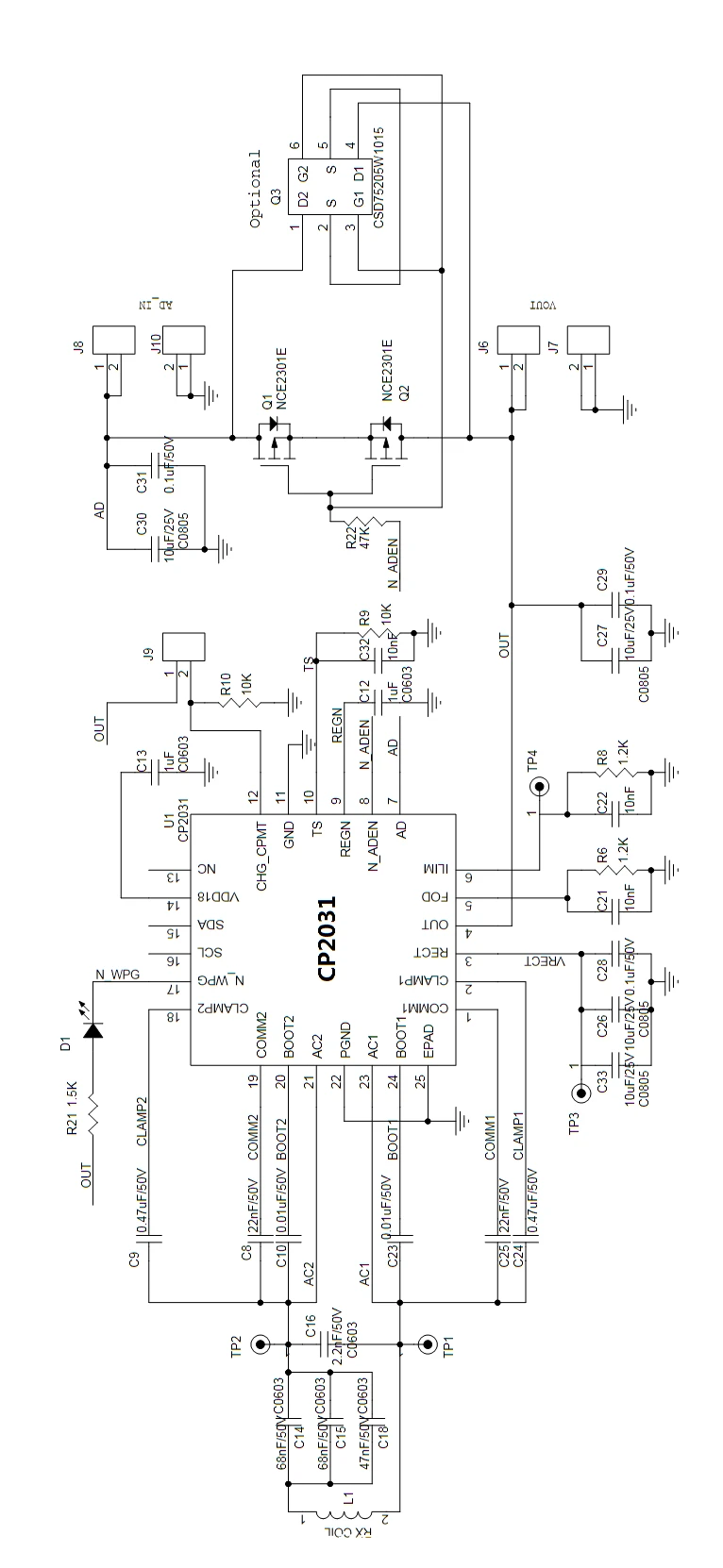

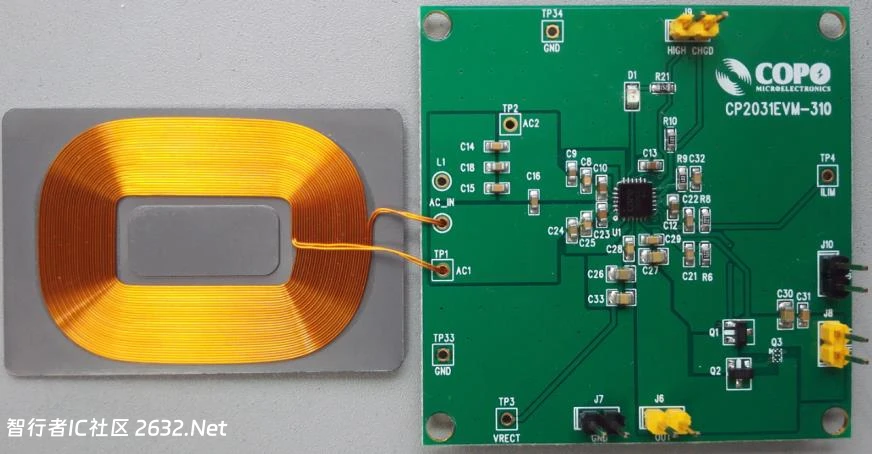

1. 电源管理类

- 涵盖DC-DC 转换、锂电池充电、开关电源、可调电源等核心电路

- 典型案例:±12V 转 ±5V 转换电路、1.5V-35V 可调直流电源、MC34063 升降压电源、12V 铅酸电池充放电监测电路

- 适用场景:嵌入式系统供电、便携设备电源设计、工业电源调试

2. 音频与信号处理类

- 包含音频功放、前置放大器、话筒放大、低失真电路等

- 典型案例:低失真 30W 音频功放、低输入阻抗音频前置放大器、超声波信号前置放大电路

- 适用场景:音响制作、语音采集设备、超声波信号调理

3. 传感器与检测类

- 覆盖超声波检测、温度报警、电流 / 漏电检测、触摸感应等实用电路

- 典型案例:超声波入侵检测器、超温报警电路、触摸开关 / 定时器、电池电流 / 欠压指示电路

- 适用场景:安防设备、环境监测、智能交互装置

4. 控制与通信类

- 包含开关控制、遥控收发、莫尔斯电码发射、内部通话等

- 典型案例:单脉冲控制转换开关、超声波遥控收发电路、30 米波段莫尔斯电码发射器、2 线内部通话器

- 适用场景:工业控制、遥控装置、简易通信设备开发

5. 其他实用电路

- 还有 LED 闪烁、MOSFET 测试、计算机电源、FM 发射等趣味 / 工程向电路

- 典型案例:LED 闪烁电路、MOSFET 电流检测电路、AT 计算机电源系列、FM 天线放大器

- 适用场景:教学演示、DIY 制作、设备调试辅助

三、资料优势

✅ 全场景覆盖:348 个电路横跨电源、音频、传感器、控制、通信等方向,满足不同项目需求

✅ 即查即用:全部为 PDF 格式原理图,无需额外软件即可打开查看,直接复用设计

✅ 新手友好:从基础电路到进阶方案都有,适合电子入门学习与进阶提升

✅ 社区专属:智行者 IC 社区整理分享,无广告、无套路,纯干货资料

四、获取方式

在智行者 IC 社区内搜索标题「348 个实用电路图大全|电子工程师速查手册」,即可获取完整资料包下载链接。

温馨提示:资料仅供学习交流使用,请勿用于商业用途。

五、写在最后

电子设计的路上,高效的资料就是生产力。希望这份 348 个实用电路图能成为你手边的「电路字典」,不管是赶项目、做实验还是自学提升,都能帮你少走弯路,快速落地想法。

后续我们还会持续更新更多硬件 / 嵌入式干货,欢迎大家在社区留言交流,一起成长为更专业的 IC 工程师!