一、说明

二、操作步骤

-

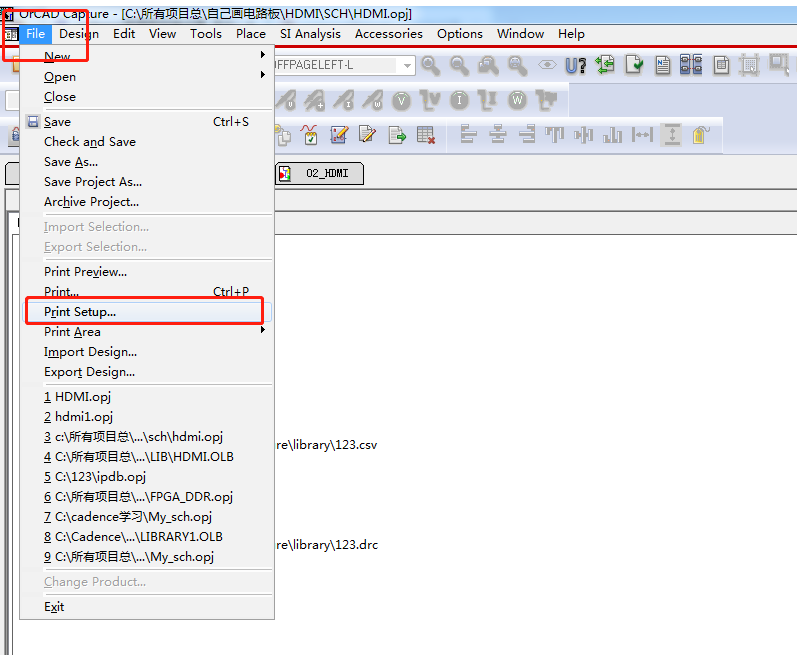

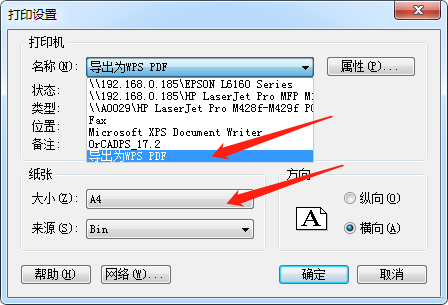

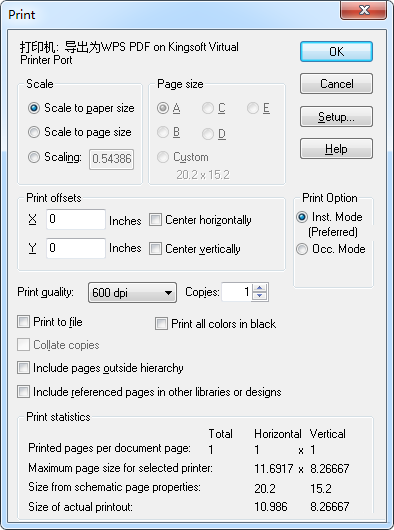

打印设置

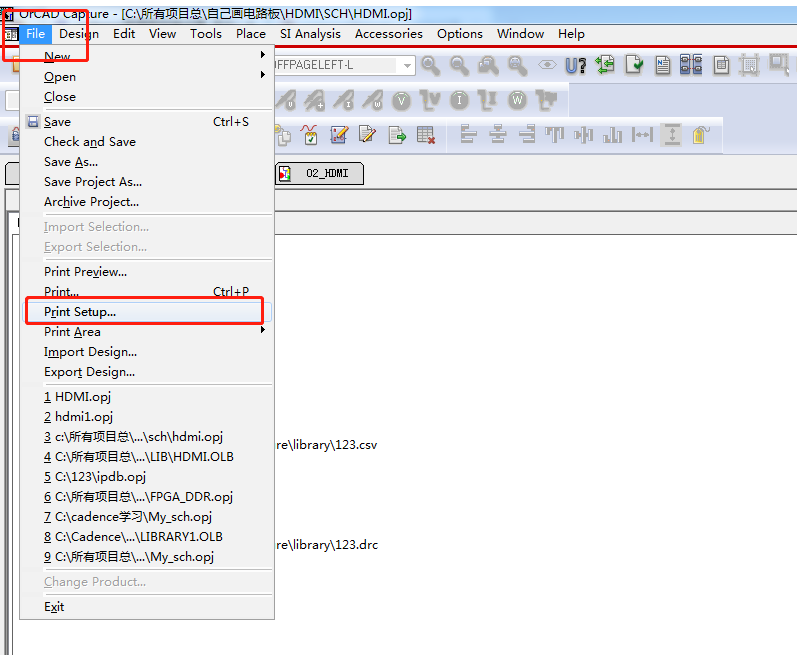

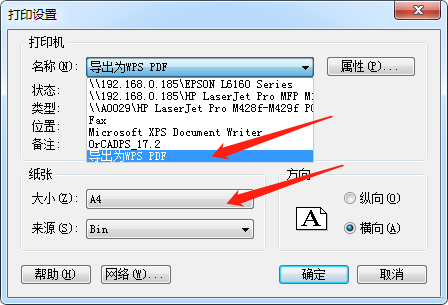

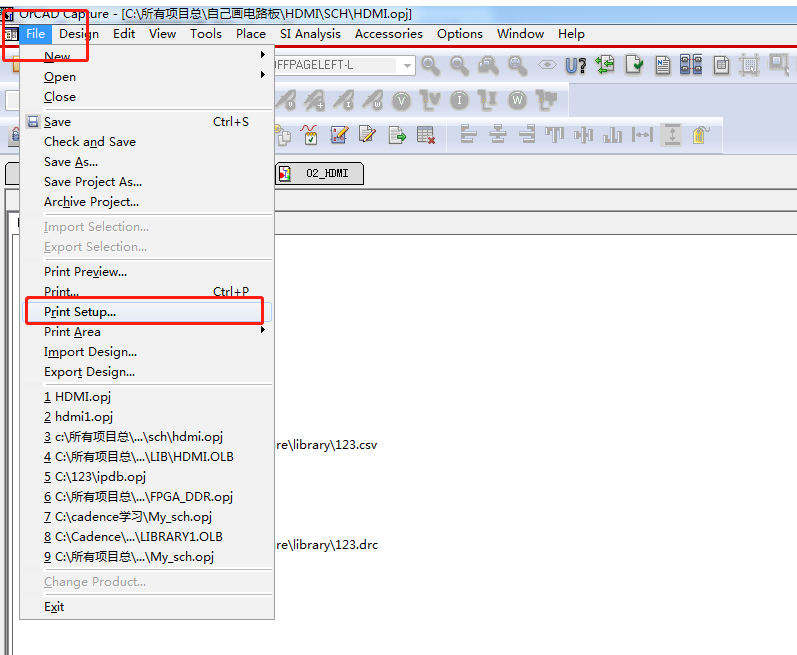

进入原理图界面,点击工具栏:

File→Print Setup选择 WPS PDF 作为打印机,完成打印格式设置。

-

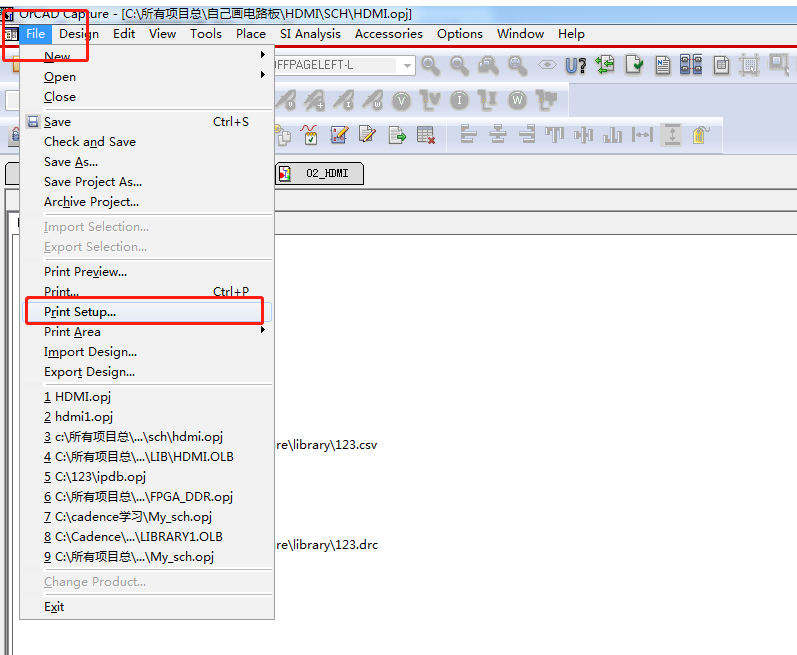

打印输出 PDF

点击:

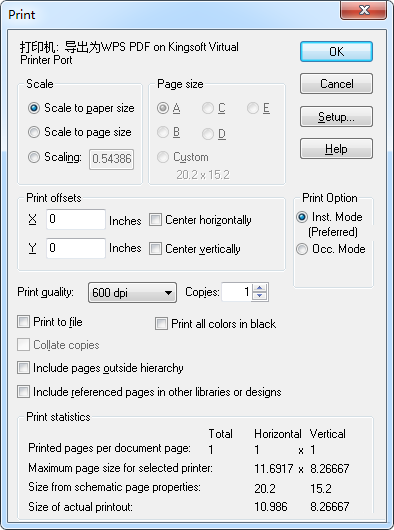

File→Print…确认打印参数,按提示选择保存路径,即可生成 PDF 文件。

三、注意事项

- 如果找不到 导出为 WPS PDF 选项,说明电脑未安装 WPS,安装后即可正常使用。

大家好!我是一名嵌入式软硬件工程师,欢迎在评论区一起学习交流~

喜欢本文可以点赞、关注,感谢支持!

专注硬件与嵌入式开发全流程工具教学,覆盖 EDA 设计、版本控制、项目管理等核心软件,从入门操作到工程化落地,系统化讲解工具链协同使用,助力高效研发与项目交付。

打印设置

进入原理图界面,点击工具栏:

File → Print Setup

选择 WPS PDF 作为打印机,完成打印格式设置。

打印输出 PDF

点击:

File → Print…

确认打印参数,按提示选择保存路径,即可生成 PDF 文件。

大家好!我是一名嵌入式软硬件工程师,欢迎在评论区一起学习交流~

喜欢本文可以点赞、关注,感谢支持!

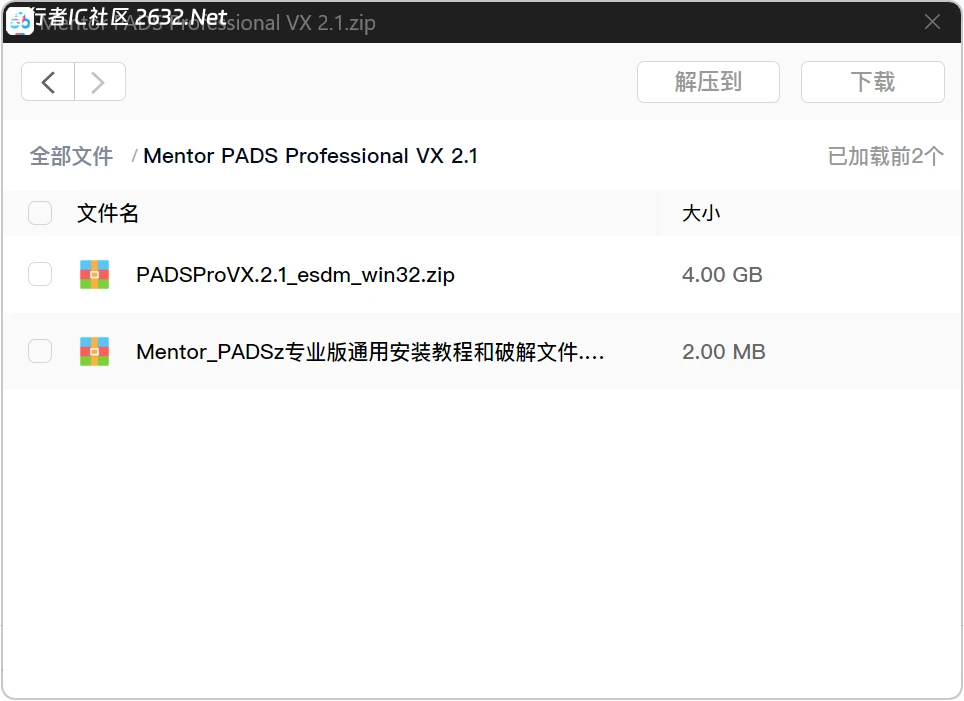

摘要: PADS Professional VX 2.1 学习版下载与使用入门。本文提供版本介绍、功能亮点、系统配置要求、安装与激活步骤、学习资源与常见问题,帮助电子工程师和学生快速上手专业 PCB 设计工具。

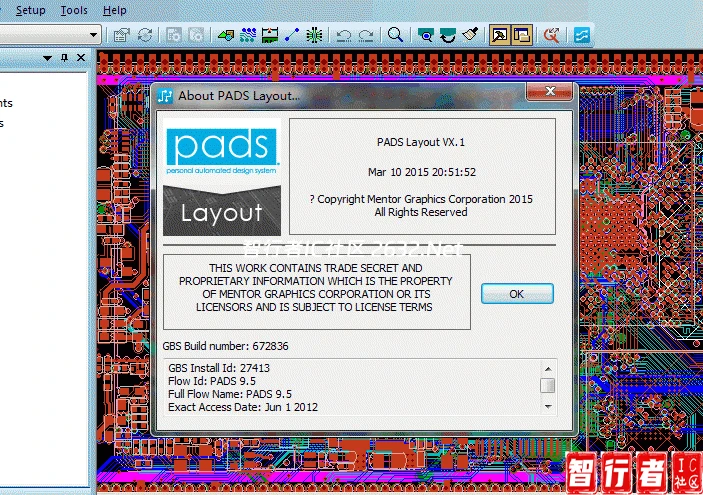

PADS Professional VX 2.1 是 Mentor Graphics(现为 Siemens EDA)旗下 PADS 系列的专业版,基于 Xpedition 技术,可完成从原理图输入、布局布线到信号/电源完整性分析和 3D MCAD 协作的一体化 PCB 设计流程。本文以“学习/教育用途”为出发点,整理下载提示、安装步骤与学习资源,便于高校师生与个人学习者参考。

最低配置:

推荐配置(更佳体验):

⚠️ 正版授权提醒:PADS 为商业软件,请通过 Siemens EDA 官方渠道或正规教育授权获取学习版或学术许可。切勿使用盗版或来源不明的安装包。未经授权使用可能带来法律风险与安全隐患。

下载后请尽量校验文件哈希(SHA256/MD5)并在干净环境中先行安装测试。

Q:可以免费长期使用学习版吗?

A:学习版通常受教育授权或试用条款限制,请以官方授权说明为准。高校可能通过集体授权为学生提供长期访问。

Q:安装后出现许可错误怎么办?

A:检查许可服务器配置、授权码有效期、防火墙或网络连接,必要时联系软件管理员或官方技术支持。

Q:如何迁移旧版工程到 VX 2.1?

A:迁移前务必备份工程。参考官方迁移文档,注意库与约束规则的兼容性。

本文仅为产品介绍与学习用途的页面模板。分享的安装包仅限于个人学习研究之用,不得用于任何商业用途,由此引发的纠纷、诉讼等事宜与本人、本站无关。为保护知识产权,如有商业需要,请与软件开发商或各代理商联系,购买正版授权。

Mentor PADS Professional VX 1.2 是西门子(Siemens)旗下 Mentor 品牌推出的专业印制电路板(PCB)设计软件,定位为 轻量化高效 PCB 设计解决方案,基于 Xpedition 企业级设计平台的核心技术简化而来,同时兼顾操作便捷性与核心设计能力,广泛适配电子工程师个人、中小企业及教育机构的中低端 PCB 设计需求。

郑重申明:

分享的安装包仅限于个人学习研究之用,不得用于任何商业用途,由此引发的纠纷、诉讼等事宜与本人、本站无关。为保护知识产权,如有商业需要,请与软件开发商或各代理商联系,购买正版授权。

作为 Xpedition Enterprise 的精简版本,该软件并非简单 “阉割”,而是针对 中小规模设计场景 进行了精准优化,核心优势体现在 “高效、易用、兼容” 三大维度:

需特别说明:其与 PADS 标准版(继承 PADS 9.5 及 PowerPCB 技术)属于不同技术分支 —— 标准版侧重传统 PCB 设计的兼容性,而 Professional 版更贴近 Xpedition 的现代化设计架构。

作为专业级工具,VX 1.2 保留了核心工程验证功能,避免设计隐患:

1.多路相同模块采用设计复用

电源输入输出链路铺铜、走线加粗

注意泄放阻容器件靠近连接器处放置,保证前后地的隔离,通道大于2mm

灯脚尽量摆一排or一列,放置美观

5.无源晶振处,电源输入铺铜打孔处理

插装器件与周围表贴器件距离尽量调开一点保持3mm(120mil)

注意原理图标识

7.四层板阻抗控制90Ω,(板厚1.6mm)可以用立创阻抗计算神器计算叠层尺寸方案

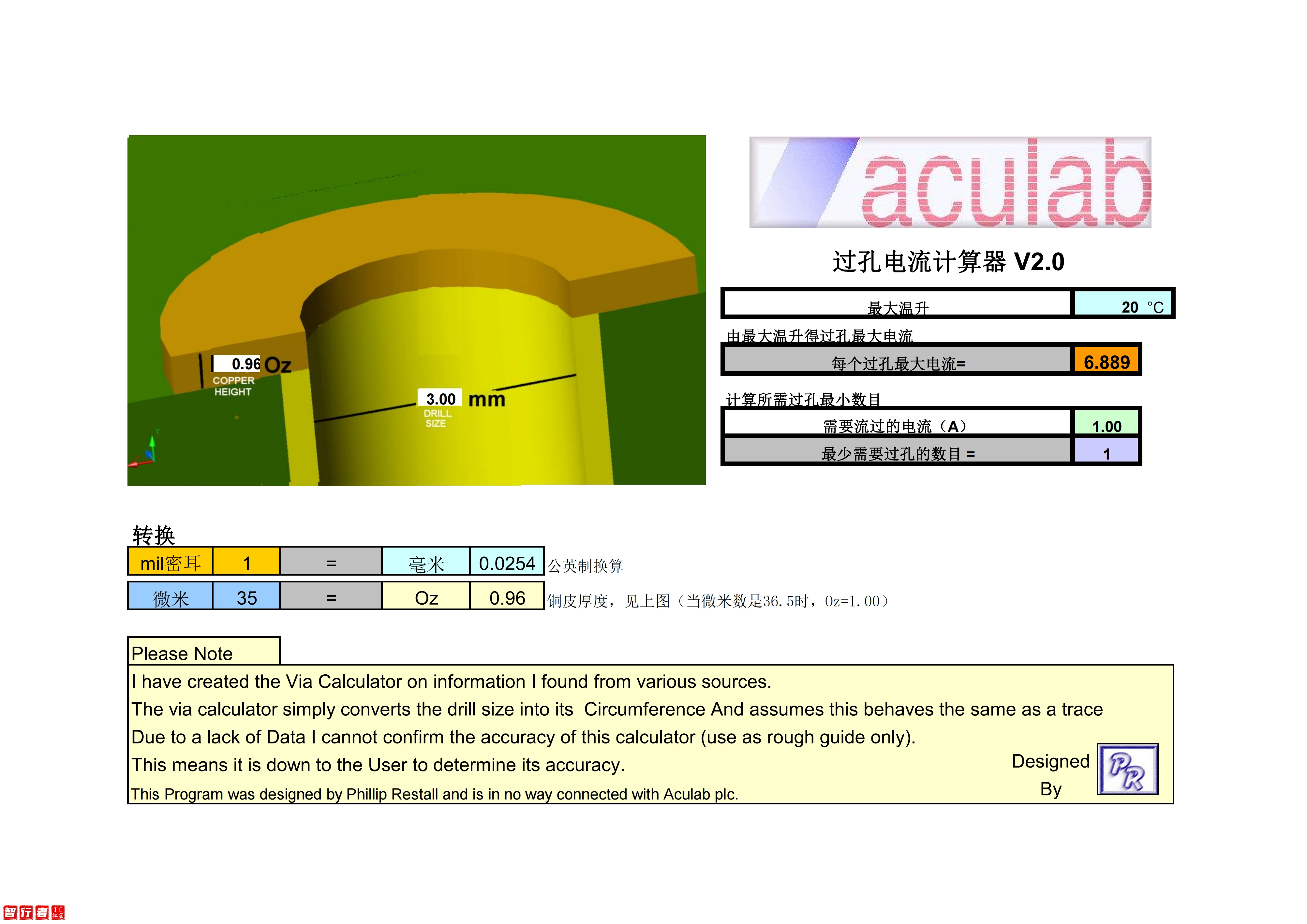

在印刷电路板(PCB)的设计与制造过程中,过孔的电流承载能力是一个至关重要的参数。它直接影响到电路的性能和可靠性。过孔电流计算器V2.0就是一款专门为解决这一问题而设计的实用工具。

从外观上看,过孔电流计算器V2.0的界面简洁明了,易于操作。在界面的显著位置,有一个直观的过孔示意图,展示了过孔的基本结构,标注了其直径等关键尺寸,如图片中显示的过孔直径为3.00毫米,孔壁厚度为0.01英寸。这有助于用户更清晰地理解过孔的物理特性与后续计算的关联。

该计算器的核心功能在于准确计算过孔的电流承载能力。在界面上方,用户可以设定环境温度,图中显示的最大环境温度为20℃,这一参数对于精确计算至关重要,因为温度会对材料的导电性能等产生影响。下方则是输入关键数据的区域,用户需要输入每个过孔最大电流值,图中显示为6.889,以及需要通过的总电流,这里为1.00安培。通过这些数据的输入,计算器能够迅速且准确地得出最少需要过孔的数目,图中显示结果为1个。

在转换功能方面,过孔电流计算器V2.0也表现得十分出色。它能够实现不同单位之间的便捷转换,例如可以将盎司(oz)与毫米(mm)进行转换,1盎司对应0.0254毫米,这种转换功能方便了工程师在不同标准和习惯下进行数据处理和设计工作。同时,还能对铜箔厚度等参数进行单位转换,如35微米的铜箔厚度对应0.96盎司,这对于PCB制造中材料参数的把控和设计优化具有重要意义。

然而,开发者也明确指出了该计算器的一些局限性。开发者Phillip Retallack说明,此计算器是基于从各种来源收集的信息创建的,只是简单地将钻孔尺寸转换为电阻和周长,并且假设其行为与走线相同。这意味着它只是一个大致的指导工具,其准确性最终需要用户自行判断。尽管如此,在实际的PCB设计工作中,它仍然为工程师们提供了一个极为有用的参考,能够帮助快速估算过孔数量和电流承载情况,节省大量的时间和精力,减少设计过程中的反复试验。

总的来说,过孔电流计算器V2.0虽然并非绝对精确,但凭借其简洁的操作、强大的核心计算功能和实用的单位转换功能,在PCB设计领域中具有很高的实用价值,是工程师们在处理过孔电流相关问题时的得力助手。

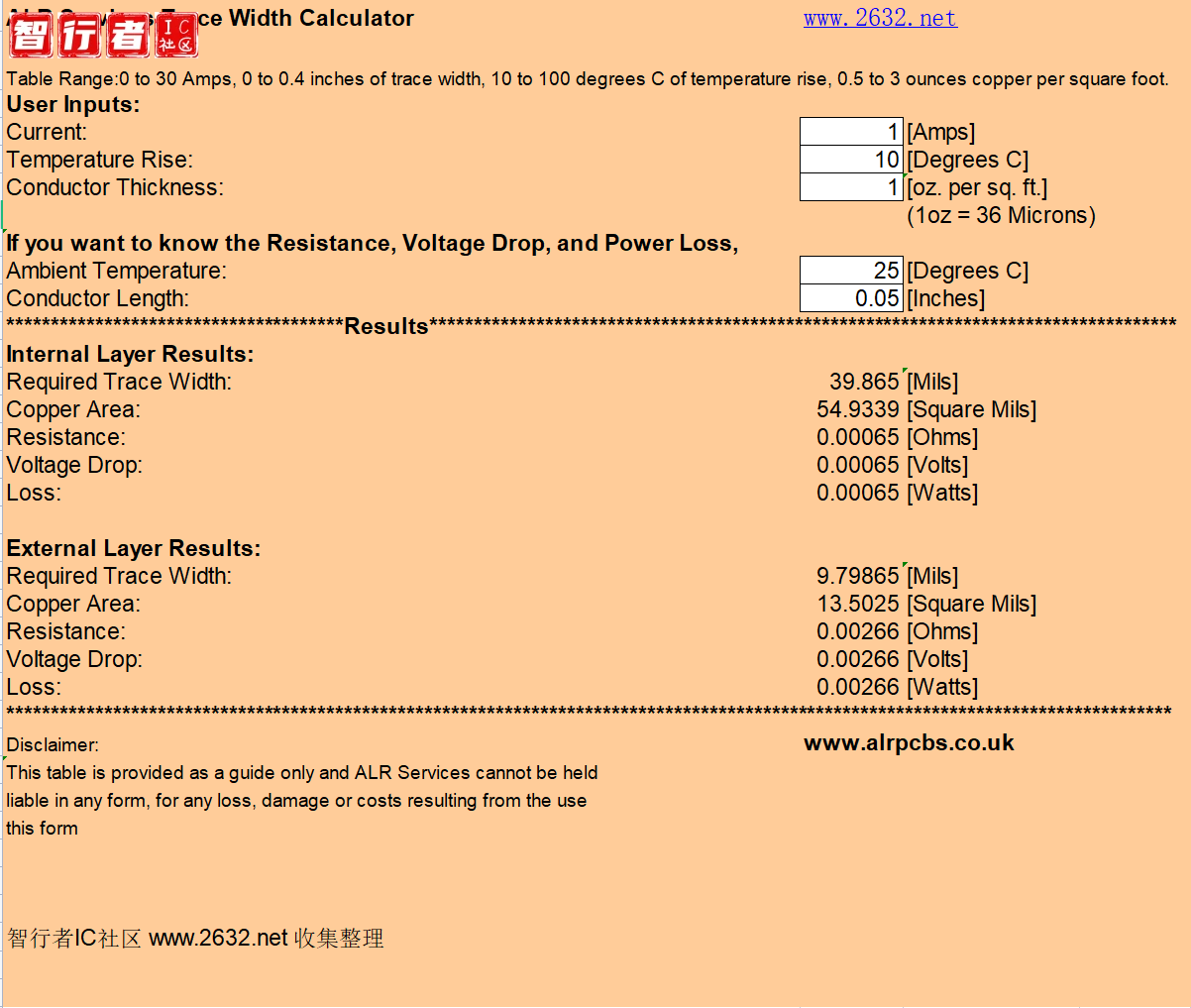

ALR Services 提供的 PCB 线宽和电流计算工具可在一定参数范围内进行 PCB 线宽等相关参数的计算。其适用范围为电流 0 到 30 安培、线宽 0 到 0.4 英寸、温度上升 10 到 100 摄氏度、每平方英尺铜厚度 0.5 到 3 盎司(1 盎司等于 36 微米)。

| 线路层类型 | 所需线宽(密耳) | 铜面积(平方密耳) | 电阻(欧姆) | 电压降(伏特) | 功率损耗(瓦特) |

|---|---|---|---|---|---|

| 内层 | 59.252 | 244.948 | 0.00015 | 0.00044 | 0.00132 |

| 外层 | 16.7025 | 69.0481 | 0.00052 | 0.00156 | 0.00469 |

| 线路层类型 | 所需线宽(密耳) | 铜面积(平方密耳) | 电阻(欧姆) | 电压降(伏特) | 功率损耗(瓦特) |

|---|---|---|---|---|---|

| 内层 | 586.185 | 1615.53 | 2.2E – 05 | 0.00027 | 0.0032 |

| 外层 | 196.426 | 541.349 | 6.6E – 05 | 0.0008 | 0.00956 |

该计算表格仅作为参考,ALR Services 对因使用此表格导致的任何损失、损坏或费用不承担任何形式的责任。在实际的 PCB 设计中,除了考虑这些计算得出的参数外,还需要综合考虑电路板的实际应用场景、散热条件、电磁兼容性等因素,以确保电路板的性能和稳定性。

评论下载:

[ceo-comment-hide]PCB过孔电流计算器PCB线宽和电流计算工具[/ceo-comment-hide]

办公新体验,高效全能更进一步

WPS Office 2019 专业增强版 是金山软件推出的一款集 文字(Writer)、表格(Spreadsheets)、演示(Presentation) 于一体的多功能办公软件套装,兼容 Microsoft Office 全系列格式,专为专业办公人士量身打造,具备更强的功能、更高的效率、更贴心的服务。

全面兼容:支持 DOC/DOCX、XLS/XLSX、PPT/PPTX、PDF 等多种主流格式,跨平台协作无障碍。

PDF 专业功能:内置 PDF 阅读、转换、合并、拆分、加密、水印等高级工具,无需额外安装软件。

增强的数据处理能力:支持超大数据量处理、VBA 宏、数据透视表、外部数据连接等高级表格功能。

演示动画更丰富:支持自定义路径动画、视频/音频插入、切换特效等,轻松制作专业级演示文稿。

批注与修订功能:多用户协作编辑更清晰,轻松应对团队办公需求。

? 插件扩展:支持丰富插件,如公式编辑器、思维导图、文档翻译等,满足更多专业场景需求。

? 多平台协同:支持 Windows、macOS、Linux、iOS、Android 等多终端同步使用,文档实时同步。

? 安全加密保障:提供企业级文档加密、防泄漏、防篡改等多重保护,保障文档安全。

? 专业模板库:海量简历、报表、PPT 模板资源,助力效率提升。

☁️ 云端办公支持:内置 WPS 云文档功能,支持文档在线存储、多人实时协作编辑。

政府/企事业单位办公

教育科研行业办公

中大型企业文档管理

需要高效办公解决方案的专业用户

与普通版本相比,WPS 2019 专业增强版 不仅解锁了更多功能限制,还在稳定性、性能、兼容性上全面提升,是个人和企业用户办公的不二之选。

| 领域 | 关键应用 | AD22专项工具 |

|---|---|---|

| 通信设备 | 5G基站/毫米波射频模块 | 阻抗匹配向导、射频参数化元件库 |

| 汽车电子 | 域控制器/车载以太网 | AUTOSAR元件模板、ISO 26262设计包 |

| 医疗电子 | 高精度生物传感器 | 低噪声布线模式、医疗级材料库 |

| 消费电子 | 折叠屏手机主板/AR眼镜微型PCB | 柔性-刚性板混合设计工具 |

| 功能维度 | AD22 | 竞品X | 竞品Y |

|---|---|---|---|

| 高速布线效率 | 12层HDI板布线时间缩短40% | 25% | 30% |

| 仿真集成度 | 内置Thermal/SI/PI/EMI工具链 | 需第三方插件 | 仅基础SI分析 |

| 中国本地化 | 全中文文档/苏州技术支持中心 | 英文为主 | 部分汉化 |

Altium Designer 22广泛应用于各种电子产品的设计领域,如通信、汽车、医疗等。它支持现代工业标准,能够满足各种复杂的设计需求。

综上所述,Altium Designer 22是一款功能强大、易于使用且广泛应用的电路设计软件。它提供了全面的设计工具、丰富的在线资源和支持以及灵活的数据管理和版本控制功能,能够帮助用户高效地完成电路设计任务。

此软件“仅限学习交流,不能用于商业用途”,如用于商业用途,请到官方购买正版软件,追究法律责任与本平台无关!

Altium Designer 24.5.1引入了旨在提高设计效率的新功能,简化工作流程,并提供更好的用户体验Altium Designer 24.5.1通过引入新功能和优化工作流程,为电子设计人员提供了更强大和灵活的设计工具。帮助他们更好地完成电子产品的设计和开发。

PS:溜溜软件中心为各位小伙伴提供到的是Altium Designer 24.5.1【附破解文件+安装教程】中文破解版软件下载,欢迎广大爱好者、设计师朋友们前来下载安装使用~

Altium Designer 24.5.1新增功能:

1. 约束管理器中的指令导入值:约束的可视化通过一个新的对话框变得更加直观,该对话框总结了约束管理器中从原理图中导入的值。此外,导入的指令可以通过其蓝色和不同的符号在设计空间中轻松区分,并且可以在Properties面板中访问相应的规则。

2. 双向E-C-O传播支持:该功能允许在约束管理器中直接从PCB创建xNet和xNet类,简化PCB和原理图端的同步。这种双向交互和同步可以极大地提高设计过程的灵活性和效率。

3.Altium Designer 24.5.1还延续了Altium Designer家族的一贯优势,例如简单,强大,现代的解决方案,包括所有原理图和PCB电子设计功能,良好的用户体验以及对独立许可模式的支持。所有编辑器(符号、包、原理图、pcb、文档等)中简单统一的用户界面使设计过程高效,避免了与手工设计同步工具相关的传统瓶颈和错误。

Altium Designer 24.5.1特点:

1.从约束管理器中的指令中导入值:约束的可视化现在更加直观,有一个新的对话框,总结了从约束管理器中的示意图中导入的值。此外,导入的指令可以通过其蓝色和独特的符号在设计空间中轻松区分,并且可以在Properties面板中访问相应的规则。通过支持在PCB约束管理器中直接创建xNet和xNet类,双向E-C-O传播简化了PCB和原理图端之间的同步。此外,为2引脚网络选择自定义拓扑会自动将其引脚作为节点添加到拓扑编辑区域,有助于更快地选择提议的xSignals。

2.创建线束设计模板:您可以在连接的Altium 365工作空间中创建、上传、编辑和重用线束接线图和线束布局图模板,从而消除多余的工作。此外,Altium Designer通过在接线图中合并对象的“type”字段,以及在布局图中合并标签和覆盖物,增强了对设计的控制,从而能够精确地管理它们在BOM中的包含。此外,您现在可以为屏蔽对象分配库ID,从而增强组织和可访问性。为了简化电线颜色定义,Altium Designer现在在接线图中使用单色参数,反映二级和三级阴影,以提高可视性和清晰度。此外,为导线对象引入的“include cut”参数使您可以控制它们在线束绘图器文档中的导线列表中的包含。

3.自动添加供电网络规则:供电网络规则在编写时自动添加到各个电网中。

4.生成odb++数据:现在可以在一次安装中选择最新的odb++ v.8.1和更早的v.7.0格式。您可以为所有已定义的变量共同或单独生成数据,从而简化您的工作流程。此外,它通过合并各种层子类型和实现区域文件支持来简化柔性/刚柔性制造。

5.防止无意的足迹镜像:为了帮助及早检测包镜像,当您使用键盘快捷键来翻转组件或房间以添加安全层时,警告对话框中的默认选项是No。PCB运行状况检查监视器的“组件”部分还添加了一个新的检查“带有镜像包的组件”选项,该选项检测放置在PCB设计空间中的组件包与适用源库中的相应包之间的引脚更改。此外,“来自PCB库的更新”工具已经增强,可以检测所有层中指标和3D实体的变化,并在“属性”选项卡上列出差异。

安装步骤

第1步

软件安装包下载解压打开(安装包有破解文件,因此下载前需关闭杀毒软件及防火墙)(注意:如果解压需要解压码的话,请换一个解压工具解压即可)

第2步

选择安装程序Installer,鼠标右键以管理员身份运行

第3步

欢迎来到软件安装向导,直接点击Next

第4步

语言选择及软件许可协议接受,首先选择语言为:Chinese 然后勾选【 l accept the agreement】,接着点击Next

第5步

选择功能组件,直接Next

第6步

软件安装位置更改,将2个安装位置都进行修改一下,可以直接在路径上更改(注意:更改安装位置不能带有中文或特殊符号),然后Next

第7步

客户体验改进计划,默认勾选【 Yes,I want to participate 】,然后Next

第8步

准备安装,直接Next

第9步

软件正在安装中,请耐心等候安装成功

第10步

软件安装成功,将运行软件的选项取消勾选,然后点击Finish

第11步

打开电脑开始菜单,找到软件拖动到桌面即可生成一个快捷方式图标

第12步

选择软件,鼠标右键打开文件所在的位置进入软件安装目录位置

第13步

打开安装包Crack\!!AD21 Unis Licenses文件夹,选择shfolder.dll破解文件复制到刚才打开的软件安装目录位置下

第14步

在电脑开始菜单找到软件打开,正在加载中

第15步

下拉选择【Add Standalone License File】

第16步

弹出窗口,找到软件安装包Crack\!!AD21 Unis Licenses\Licenses里面的AD23-Sandy_ScienceTeam_1.alf打开

第17步

此时就可以看到软件破解成功了,可以使用到2030年11月5号

第18步

点击右上角的设置图标

第19步

勾选【Use localized resources】,弹出对话框,点击OK

第20步

点击Apply-OK

第21步

重新打开软件,进入软件界面,此时就是中文破解版的了,可以放心使用~(ps:如果你觉得不错的话,请给我一个好评啦~)

Cadence PCB设计环境(包括Allegro和OrCAD)的快捷键设置通常保存在以下文件中:

%CDSROOT%\share\pcb\text\env$CDSROOT/share/pcb/text/env%HOME%\pcbenv\env~/.pcbenv/env您可以从以下渠道获取预定义的快捷键配置文件:

以下是env文件中常见的快捷键配置段落:

# 视图控制快捷键

alias ~F1 "zoom in"

alias ~F2 "zoom out"

alias ~F3 "zoom fit"

# 常用工具快捷键

alias ~P "add connect"

alias ~V "vertex"

alias ~D "delete"

# 层控制

alias ~L "change layer"

# 测量工具

alias ~Q "show measure"

cp env env.bak

alias <快捷键> "<命令> <参数>"alias CtrlShiftA "angle 45"

alias ~W "zoom fit; redraw"

alias ~R "if(axlIsAlias("~R")) then funckey ~R else funckey ~R 'redraw'"

[ceo-payment-hide sku=”1″]# # ALLEGRO GLOBAL Environment file # # The following variables are set by the software if not preset by user: # CDS_SITE, ALLEGRO_SITE, TELENV, ALLEGRO_INSTALL_DIR, # ALLEGRO_INSTALL_TOOLS, ALLEGRO_INSTALL_ROOT, ALLEGRO_TYPE, # __UNIX (if UNIX), _PROGRAM, HOME # # You may set the Operating System variable: # ALLEGRO_PCBENV # to overwrite the default of the user’s pcbenv directory. This variable # must be set at the OS level and has no effect if set in an Allegro env file. # The directory given must exist. If no directory is found the system will # fallback to its default location. # # The following variables are preset at startup, direct settings in env # files will be overridden # LOCALENV: seeded based upon /pcbenv (or if set ALLEGRO_PCBENV) # LOCALPATH: seeded based upon . LOCALENV, ALLEGRO_SITE, GLOBALPATH # Variable names are case insensitive #——————————————————————– # System Variables set GLOBAL = $ALLEGRO_INSTALL_DIR/text # change from LIBPATH because it conflicts with IBM’s shared library # environment variable set ALIBPATH = $ALLEGRO_INSTALL_DIR/pcb_lib set COMPLIBPATH = $ALLEGRO_INSTALL_DIR/allegrolib set GLOBALPATH = . $GLOBAL # Allegro Data Services Variable set ADSPATH = $GLOBALPATH # Present for compatiblity with older versions of Allegro. ifnvar ALLEGRO_SITE “set ALLEGRO_SITE .” ifnvar CDSPLAT “set CDSPLAT ” ifnvar ALLEGRO_INSTALL_DLL “set ALLEGRO_INSTALL_DLL ” #——————————————————————– # Configuration variables (Don’t change) set BMPPATH = . $ALLEGRO_SITE/icons $GLOBAL/icons set FORMPATH = . $ALLEGRO_SITE/forms $GLOBAL/forms set MENUPATH = . $ALLEGRO_SITE/menus $GLOBAL/cuimenus set MATERIALPATH = . $LOCALENV $ALLEGRO_SITE $GLOBAL #Configuration paths set PRFEDITPATH = . $LOCALENV/configure/prfedit $ALLEGRO_SITE/configure/prfedit $ALLEGRO_INSTALL_DIR/configure/prfedit set BATCHHELPPATH = . $ALLEGRO_INSTALL_DIR/batchhelp set SPROUTEPATH = $ALLEGRO_INSTALL_DIR/configure/sproute set HELPPATH = . $ALLEGRO_INSTALL_DIR/help $GLOBAL/help set PDFPATH = . $ALLEGRO_INSTALL_DIR/help/pdf # Graphics demo env set IMAGEPATH = . $ALLEGRO_INSTALL_DIR/examples/image # Allegro Plugin search path set AXLPLUGINPATH = . $LOCALENV/$CDSPLAT $ALLEGRO_SITE/$CDSPLAT $ALLEGRO_INSTALL_DLL #——————————————————————– # Drawing font set VECTORFONTPATH = . $GLOBAL set ANSIFONT = ansifont set KANJIFONTPATH = . $GLOBAL/fonts/kanji set KANJIFONT1 = kanjifont1 set KANJIFONT2 = kanjifont2 #——————————————————————– # Display Variables set display_backingstore on # disable repair under ratsnests set display_shapefill_analysis 1 #——————————————————————– #——————————————————————– set compalib = $ALIBPATH/symbols $COMPLIBPATH/symbols set topfilelib = $ALIBPATH/templates $COMPLIBPATH/templates set signal_install_dir = $ALLEGRO_INSTALL_DIR/signal set signal_optlib_dir = $signal_install_dir/optlib # HDL Supported Design Library Search Path Variables set MODULEPATH = . $ALLEGRO_SITE/modules set TILEPATH = . $ALLEGRO_SITE/modules set WBPATH = . $ALLEGRO_SITE/wbtiers set PADPATH = E:/via/ E:/Project/shoufang/vt4k_encoder_7A200T_2016_08_12/LIB/ set PSMPATH = E:/via/ E:/Project/shoufang/vt4k_encoder_7A200T_2016_08_12/LIB/ set DEVPATH = E:/via/ E:/Project/shoufang/vt4k_encoder_7A200T_2016_08_12/LIB/ set TECHPATH = . $ALLEGRO_SITE/tech $GLOBAL/tech set PARAMPATH = . $ALLEGRO_SITE/parameter set TOPOLOGY_TEMPLATE_PATH = . templates .. ../templates $ALLEGRO_SITE/topology $topfilelib # SigNoise data installation directory set SIGNOISEPATH = . $LOCALENV $ALLEGRO_SITE/signal $signal_install_dir $signal_optlib_dir $GLOBAL # SigNoise model variables. set SI_MODEL_PATH = . $ALLEGRO_SITE/signal $signal_install_dir set SI_MODEL_FILE_EXT = Generic_IBIS(ibs) IBIS_Buffer(buf) IBIS_EBD(ebd) IBIS_ICM(icm) IBIS_Pin_List(pin) IBIS_Package(pkg) Quad(mod) Generic_SPICE(spc) HSpice_Input(sp) HSpice_Output(lis) Spectre(spc) Touchstone(S?p,s??,snp) DML(ndx,dml) Interconnect(iml) ABIML(abiml) #——————————————————————– # Non-HDL Supported Design Search Path Variables set MISCPATH = . $ALLEGRO_SITE/misc set ARTPATH = . .. $ALLEGRO_SITE set APTPATH = . .. $ALLEGRO_SITE set CLIPPATH = . set DCLPATH = . .. $ALIBPATH $COMPLIBPATH set DEVPATH = . devices .. ../devices $ALLEGRO_SITE/devices $ALIBPATH/devices $COMPLIBPATH/devices set DFAAUDITPATH = . $ALLEGRO_SITE/assembly $ALLEGRO_INSTALL_DIR/assembly set DFACNSPATH = . dfa .. ../dfa $ALLEGRO_SITE/dfa set NCDPATH = . .. $ALLEGRO_SITE/nclegend $GLOBAL/nclegend set SCRIPTPATH = . $ALLEGRO_SITE/scripts $GLOBAL/script set TEXTPATH = . $ALLEGRO_SITE/extracta $GLOBAL/views set VIEWPATH = . $ALLEGRO_SITE/views set XTALK_TABLE_PATH = . xtalk_tables .. ../xtalk_tables $ALLEGRO_SITE/xtalk $ALIBPATH/xtalk_tables set WIZARD_TEMPLATE_PATH = . $ALLEGRO_SITE/new_templates $ALLEGRO_INSTALL_DIR/pcb_lib/symbols/template set LDFPATH = . # System Configuration .scf file search path set SCFPATH = . scfs .. ../scfs # Display the headsup meter in a fixed position in the control panel. set allegro_dynam_timing_fixedpos # For IC Packaging tools (APD and SiP tools), the following defaults the # HUD for the wirebond tools to updating 25 times per second. set wirebond_hud_update_frequency 25 # By default, suppress bond wire DRCs that are 3D in nature but being # checked in 2D. By default, the APD/SiP tools will only report wire # violations if they occur over top of the end item (finger or pin) and # the two wires are on different nets. set wirebond_suppress_bondwire_drcs #——————————————————————– #——————————————————————– # alias # May use function keys F2-F12, most Alpha-numberic keys with control # modifier (although Control – C, V and X are reserved for copy, paste and cut) # and Navigation Keys (Home, Up arrow, Esc, etc.) These items may be modifed # by the following: # Modifier Indicator Example # Shift S SF2 # Control C (function keys) CF2 # Control ~ (alpha-numeric) ~N # Meta A AF2 # Modifiers may be combined. Some examples: # CSF2 Control-Shift F2 # ASF2 Meta-Shift F2 # CAF2 Control-Meta F2 # CASF2 Control-Meta-Shift F2 # ~SZ Control-Shift Z # SUp Shift-Up Arrow # CUp Control-Up Arrow # # funckey # use the funckey when you wish to have alphanumeric keys operate # like the Function keys when the cursor is in the Allegro canvas. # # Example — following starts the move command without a Enter key # funckey m move #——————————————————————– # Bind roam operations to function keys set roamInc = 96 alias Up “roam y -$roamInc” alias Down “roam y $roamInc” alias Left “roam x -$roamInc” alias Right “roam x $roamInc” # Bind incremental pick by grid unit functions to ctrl and shift–arrow keys alias CUp “ipick 0; ipick_to_gridunit 0 +1” alias CDown “ipick 0; ipick_to_gridunit 0 -1” alias CLeft “ipick 0; ipick_to_gridunit -1” alias CRight “ipick 0; ipick_to_gridunit +1” alias SUp “move; ipick_to_gridunit 0 +1” alias SDown “move; ipick_to_gridunit 0 -1” alias SLeft “move; ipick_to_gridunit -1” alias SRight “move; ipick_to_gridunit +1” # example of a funckey to emulate Layout capability # The “-cursor” option can be added to any Allegro command with the pick familty # and we utilize the position under the cursor when the command is execute. So # this example would center the display to position under the cursor when the ‘c’ key # is pressed. # funckey c “zoom center; pick -cursor” #——————————————————————– # F1 is normally reserved by the system for Help so we don’t use it alias F2 zoom fit alias F3 next alias F4 show element alias F5 redraw alias F6 done alias F7 next alias F8 oops alias F9 cancel alias F10 grid toggle alias F11 zoom in alias F12 zoom out alias SF2 property edit alias SF3 slide alias SF4 show measure alias SF5 copy alias SF6 move alias SF7 dehilight all alias SF8 hilight pick alias SF9 vertex alias SF10 save_as temp alias SF11 zoom previous alias SF12 zoom world alias CF2 next alias CF5 color192 alias CF6 layer priority alias CSF5 status alias ~N new alias ~O open alias ~S save alias ~D delete alias ~Z undo funckey + subclass -+ funckey – subclass — funckey 1 assign color funckey 2 undo funckey 3 copy funckey 4 change funckey 5 dehilight funckey 6 swap components funckey 7 swap functions funckey 8 zoom points funckey a zoom out funckey b rotate funckey c delete funckey d add connect funckey e shape edit boundary funckey f slide funckey g move funckey h add line funckey m custom smooth funckey n mirror funckey q rats net funckey o unrats net funckey r shape select funckey s zoom in funckey t shape add funckey u island_delete funckey v toggle funckey w delay tune funckey z show measure alias Esc done funckey ” ” iangle 90 funckey F3 drc update funckey T “prepopup; pop dyn_option_select ‘Snap pick to@:@Segment Vertex’” funckey E “prepopup; pop dyn_option_select ‘Snap pick to@:@Arc/Circle Center’” funckey R “prepopup; pop dyn_option_select ‘Snap pick to@:@Pin’” #——————————————————————– # OTHER ALIASES alias edps padedit alias rps “replace padstack” alias unplrp report unplaced alias x pick alias y pick l alias ix ipick alias iy ipick 0 alias reopen ‘open -q $module’ alias revert ‘open -q $module’ # autoroam alias sar set pcb_autoroam alias uar unset pcb_autoroam alias reopen ‘open -q $module’ alias bubset ‘settoggle shove_mode Off “Hug preferred” “Shove preferred”; options bubble_space $shove_mode’ alias ~B bubset alias smoothset ‘settoggle smooth_mode Off Minimal Full; options smooth_level $smooth_mode’ alias ~C smoothset #——————————————————————– # COMMAND DEFAULTS # allow slide to work on arcs by default set slide_arcs # Compatibility aliases alias window zoom alias hilite hilight alias dehilite dehilight alias pickx pick alias picky pick l alias ipickx ipick alias ipicky ipick 0 alias cdnshelp cdsdoc #——————————————————————– # MOUSE WHEEL SUPPORT (Windows only) # Environment Variables – Note quote variables so they are evaluated # at button time not when this file is read. # – _wheelcnt variable is set based upon number of detents wheel moved # range is -4 to 4 (no 0) # – sx1 and sy1 are cursor coordinates when wheel is moved # # Button values # wheel_up: when wheel is moved up # wheel_down: when wheel is moved down # wheel: up/down if either of above 2 buttons are not assigned # # Keyboard modifiers (note we are case insensitive) # S – shift key # C – control key # SC – shift and control # Example: SCwheel – for wheel button assignment with both shift & control keys # # Button factor may be factorion (e.g. 0.5) set buttonfactor = 1 button wheel_up “zoom in $buttonfactor” button wheel_down “zoom out $buttonfactor” button Cwheel_up “zoom in $buttonfactor” button Cwheel_down “zoom out $buttonfactor” # The parameter “BGA*_*” is used when you press the keyboard ” Ctrl/Shift + Up”. # But the value will take effect only when these codes such as “set BGA1_27 = 1.27” are the latest. # If you want to use “set BGA1_27 = 50” you must move it to “set BGA1_27 = 1.27 ” behind. # Unit:millimeter set BGA1_27 = 1.27 set BGA1_0 = 1.0 set BGA0_8 = 0.8 #set BGA0_8 = 3.81 # Unit: mil set BGA1_27 = 50 #set BGA1_0 = 25.5900 set BGA1_0 = 39.37 #set BGA0_8 = 31.5 set BGA0_8 = 31.49 #set BGA0_8 = 150 alias Up ipick 0 $BGA1_27 alias Down ipick 0 -$BGA1_27 alias Left ipick -$BGA1_27 0 alias Right ipick $BGA1_27 0 alias CUp ipick 0 $BGA1_0 alias CDown ipick 0 -$BGA1_0 alias CLeft ipick -$BGA1_0 0 alias CRight ipick $BGA1_0 0 alias SUp ipick 0 $BGA0_8 alias SDown ipick 0 -$BGA0_8 alias SLeft ipick -$BGA0_8 0 alias SRight ipick $BGA0_8 0 source -q $ALLEGRO_SITE/site.env ### User Preferences section ### This section is computer generated. ### Please do not modify to the end of the file. ### Place your hand edits above this section. ### set undo_depth = 30 set padpath = E:/via/ E:/IPTV/LIB/ set psmpath = E:/via/ E:/IPTV/LIB/ set devpath = E:/via/ E:/IPTV/LIB/ set allegro_dynam_timing = on unset allegro_etch_length_on set allegro_dynam_timing_fixedpos unset no_dynamic_zoom unset no_zoom_to_object unset viewer_useoglgraphics unset draw_etch_outline unset disable_opengl set no_dragpopup unset display_nodynamicarcwidth unset display_drcfill unset old_style_flash_symbols unset ratt_off_if_connected unset display_thintext unset display_nolinewidth set infinite_cursor_bug_nt set pcb_cursor = infinite set showmeasure_altunits = millimeters set nolast_directory set nolast_file set display_nohilitefont set logic_edit_enabled unset telskill set autosave_time = 10 set autosave unset old_shape_fill_style unset no_shape_fill [/ceo-payment-hide]

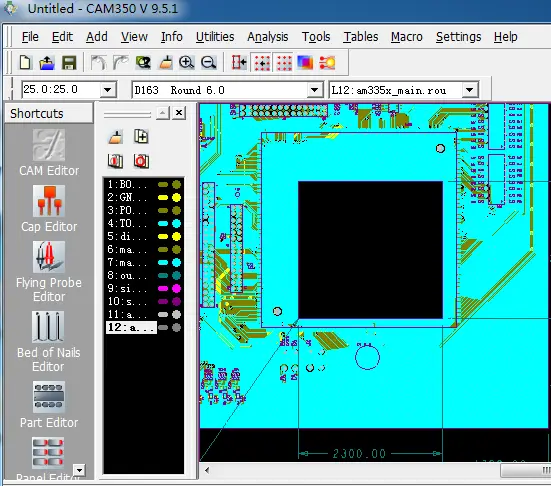

CAM350_951 是一款专业的PCB(印刷电路板)设计制造分析软件,主要用于PCB制造前的工程审查、优化和数据处理。