于内容创作以及专业工作范畴之内,检查跟输出属于决定成果质量的最终关卡。好多人耗费大量时间去构思并制作,然而在最后环节却敷衍了事,致使小错误频繁出现,进而影响整体效果咧。掌握专项场景中的检查技巧,建立规范的输出流程,能够帮你规避低级错误,提升作品的专业度。

检查时最容易忽略哪些细节

处于检查之中,格式一致性属于极容易招致被忽视情形的一环。看看字体大小是不是统一的,瞧瞧段落间距是否保持一致,瞅瞅标点符号有没有全角半角混合使用。像这些细节,纵使表面看似甚是微小,然而却能够直接对阅读体验产生影响。我有过这样的经历,曾目睹了一份准备尤其精心的报告,仅仅是因为标题字体没有做到统一,从而给人遗留下不专业的印象。在此给出建议,在实施检查的时候特意专门留出一回审视,仅仅专注于格式方面的问题。

常被忽略的还有数据准确性,与此相关的引用来自何处。数字有没有进行核对,引用是不是有出处可查,一旦这些方面出现差错,可信度会遭受严重削弱。尤其是碰到具体数字、日期以及人名的时候,最好逐个去核对原始资料,别凭借记忆来做判断。

如何建立自己的输出检查清单

工作性质所决定,构建个性化检查清单乃是提升效率的关键所在。写作类别之中,涵盖错别字查验、语法通顺与否、逻辑连贯状况、观点明确程度诸般条目;设计类别方面,则着重关注色彩搭配成效、元素对齐情形、分辨率适配状况等。清单务必具体且具可操作性呢,像“核查所有超链接是否具备有效性”这般,而非仅仅是笼统的“检查链接”这种表述呀。

进行分层次检查会具备更全面的特性,第一遍着重关注整体结构以及核心内容,第二遍着手处理细节与格式,第三遍模拟读者视角去体验。每次仅仅专注于一个层面,防止因多任务处理而致使出现遗漏。要将检查清单予以保存,并在实际运用过程中持续优化,把不必要的项删除,增添容易遗漏的项。

输出前的最后一道防线是什么

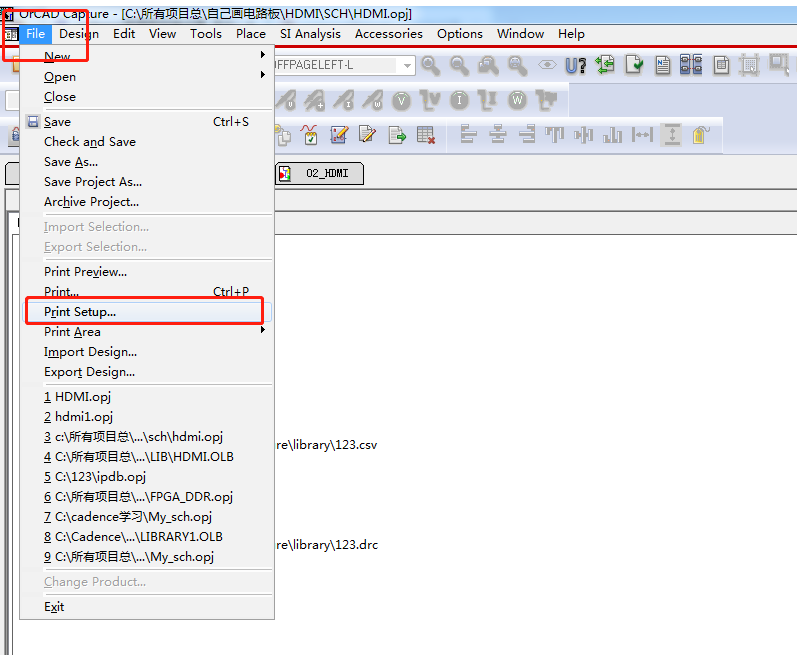

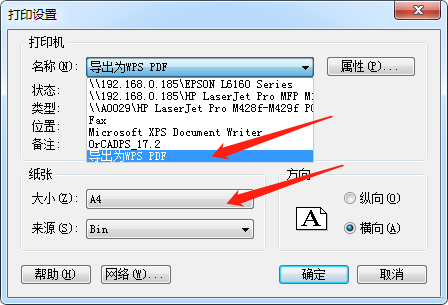

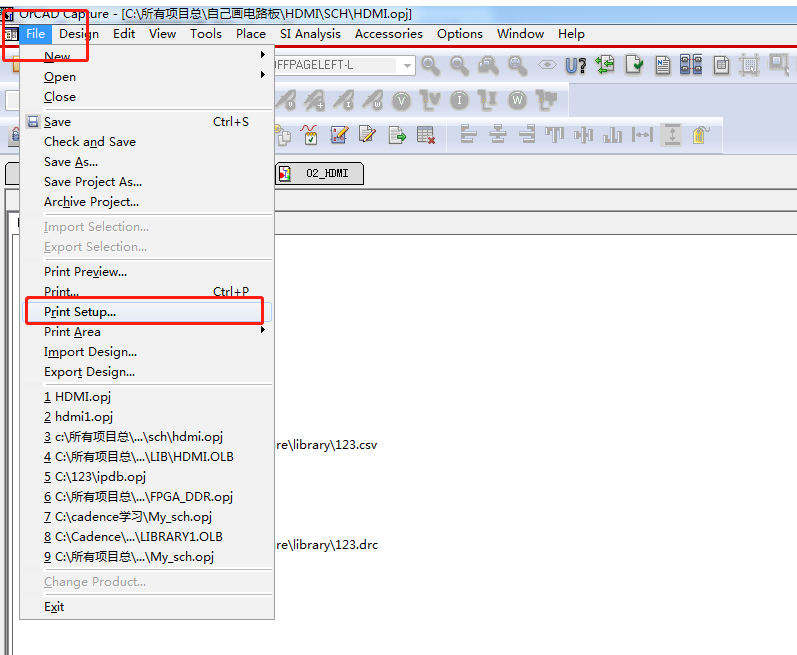

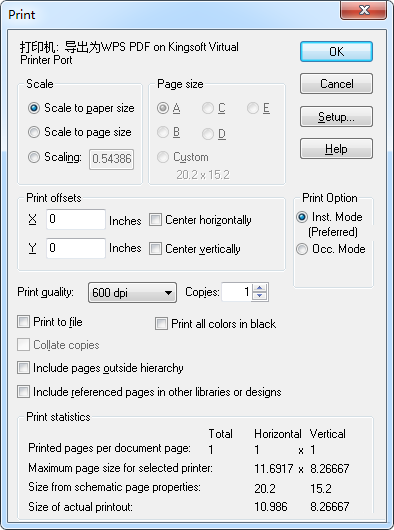

最终的把关要点归属输出格式以及媒介适配。相同的内容,打印出来观看与在屏幕上显示的效果全然不一样。当准备输出纸质版之际,需要检查页面设置以及打印预览;而准备发布到网络平台之时,要预览移动端的显示效果。不同的平台对于图片尺寸、文件大小有着各异的要求,务必要提前去确认。

备份以及版本管理同样是相当关键的,在输出之前务必要确认你所使用的是最终版本,防止将修改了一半的草稿发送出去,对于重要文件而言建议输出两种格式,例如同时保存PDF格式以及原始文件,以此方便后续进行修改,文件的名称应当包含版本号以及日期,避免出现像“最终版”“最终版2”这种混乱的命名方式。

怎样让检查成为习惯而非负担

把检查融汇进工作流程之中,并非当作额外的任务,每完成一个模块便进行简易检查,最后再整体浏览一遍,如此这般分散检查压力,而且更易于察觉问题,运用工具予以辅助,像拼写检查、格式刷、样式模板等,则能够减轻人工检查的工作量。

养成间隔着去做检查的习惯,,在完成初稿之后,不妨先搁置一旁,去喝上一杯水,亦或是去处理别的事务,等回来再去看初稿,常常能够察觉到之前被忽略掉的问题 ,要是条件许可的话,请求同事来帮忙进行交叉检查,从新的视角来看越发容易发现存在的盲点 ,要记住,检查并非是自我怀疑,而是对作品负责的一种呈现。

每日工作里头,你可有啥与众不同的检查法子呀?欢迎于评论区域分享你的经历,点赞以便让更多人瞧见这些实用的窍门呢。