第一天

1.注意事项

(1)Pcb比较重要的特性

1、可制造性 DFM(做产品和搞科研的区别)

2、信号完整性 SI

3 、电源完整性 PI

4 、电磁兼容性 EMC

5 、热设计

6、可维修性

(2)使用软件

原理图工具:Orcad

PCB工具:Allegro

全球最大的电子设计自动化(Electronic

DesignAutomation)、半导体解决方案和

设计服务供应商

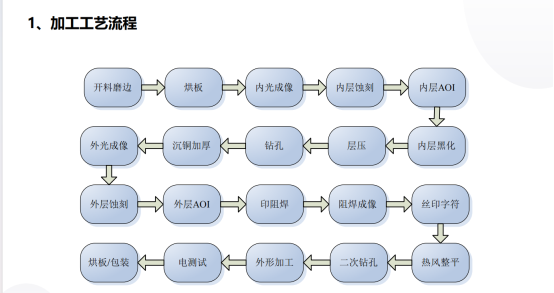

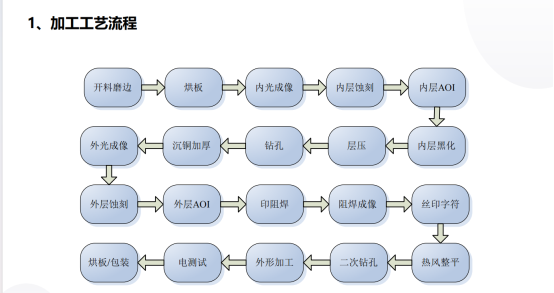

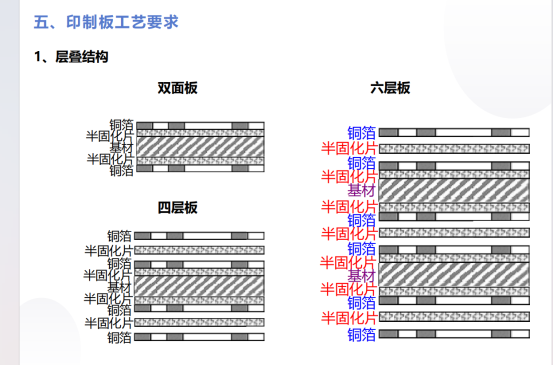

(3)必会的 pcb的加工流程/工艺流程 先内后外

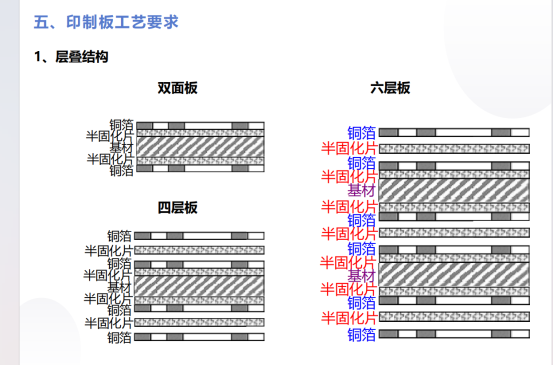

(4)必会

(5)注意:1 OZ铜厚的定义为1 平方英尺面积内

铜箔的重量为一盎(ang)司,对应的物理厚度为35um(1.378mil);

5.16 第二天

1.注意事项

(1)

(1.1)pcb封装的相关操作软件

(1.2)原理图的相关操作软件

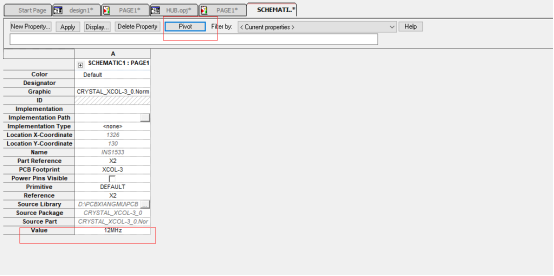

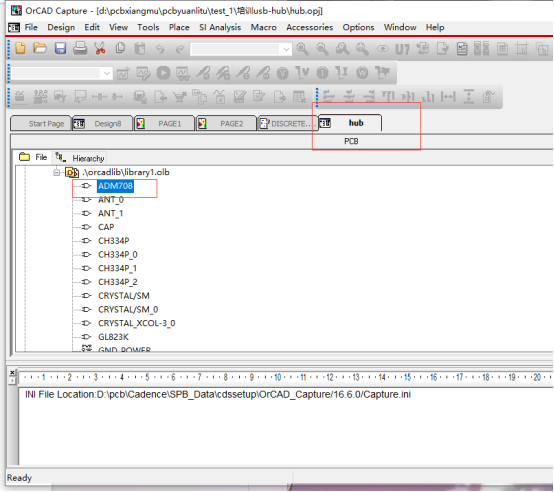

(2)原理图设计软件的使用

(2.1)首先 在 开始 菜单 找到 CIS 然后选择第一个 并把 左下角的 对钩 勾上

(2.2)

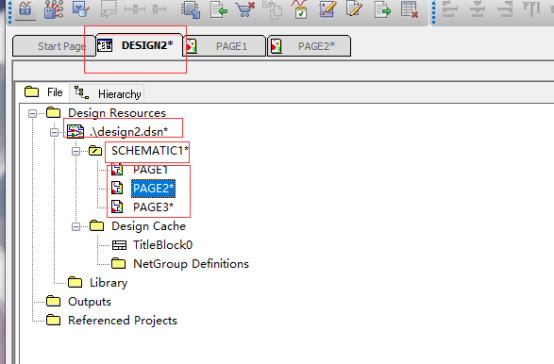

New design 新设计 new project 新项目

(2.2.1) 新设计

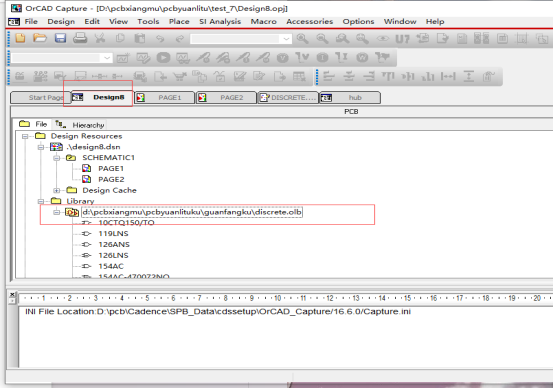

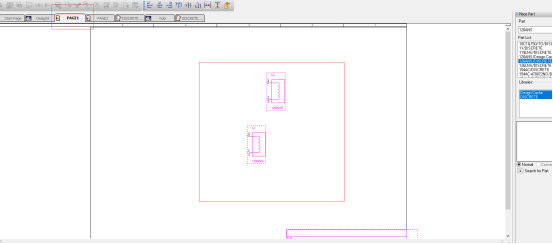

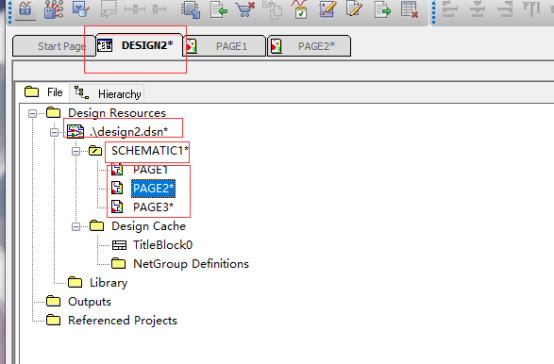

点击 new design 然后找到design页面 右键.dsn文件 save as 保存文件

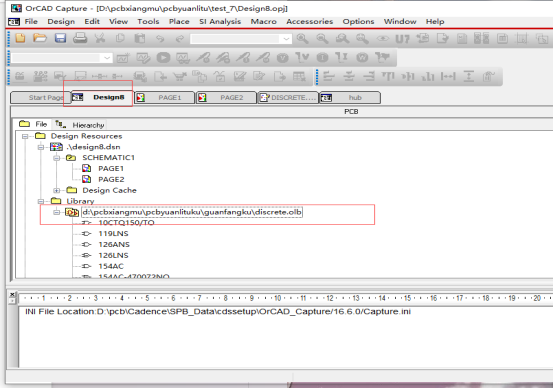

(2.2.2) 展开.dsn文件

会找到SCHMATIC1文件 右键可以创建 新的page页面 右上角带星号的表示没保存(可以在最上方的工具栏选项 点击保存 右键该文件名可以进行重命名等操作)

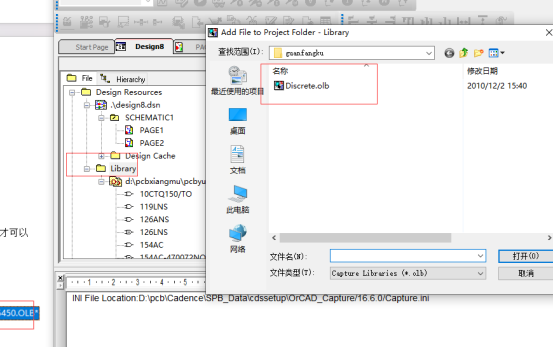

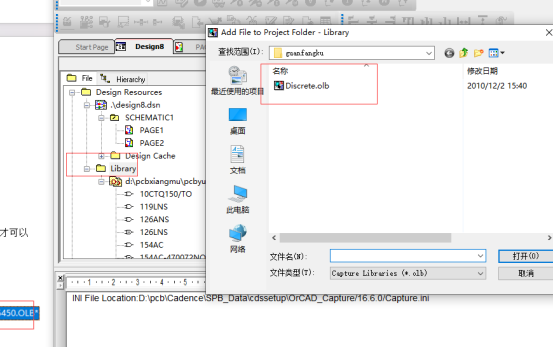

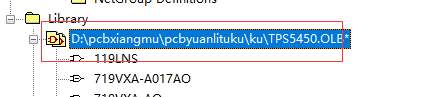

(2.3)库的操作 –库用来存放所有 要画的元器件 –没有则需要自己画

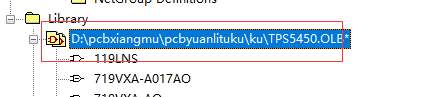

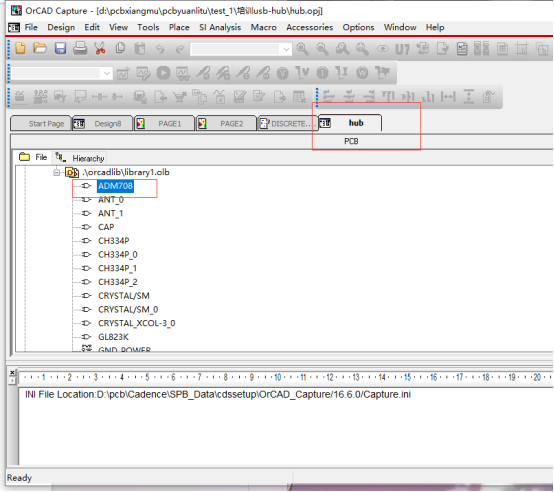

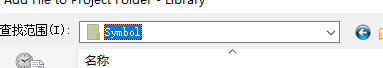

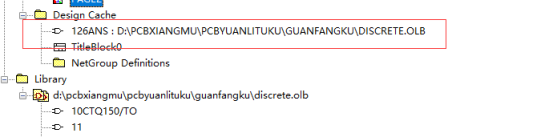

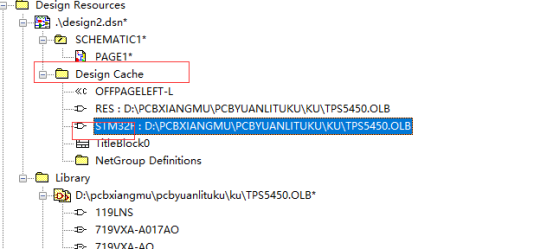

右键选中Library 选择add file 然后 找到该文件夹(D:\课程\20240319\Symbol) 然后选中里面的所有.OLB文件 打开

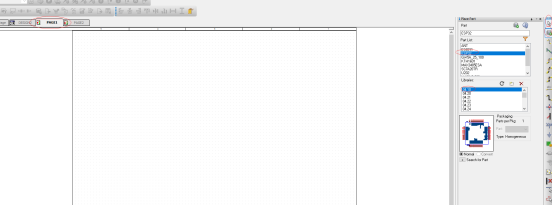

(2.3.1)小案例 先选中page1 然后选中 箭头图标和加号图标 再 选择 04.10 ESP32

然后双击ESP32 即可将图形放在页面中 然后单机确认 当确认完成后即可 右键 选择end mode即可 (同理想要删除 则单机图像 右键选择 delete 即可)

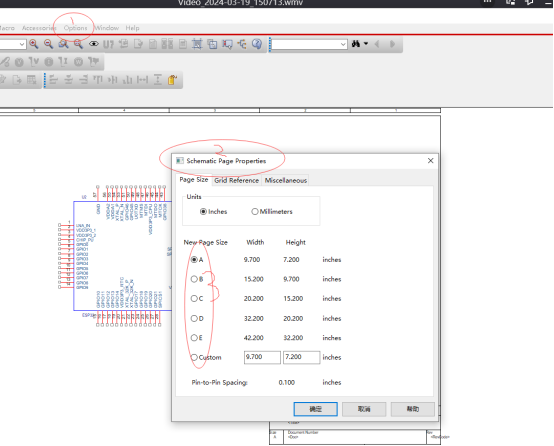

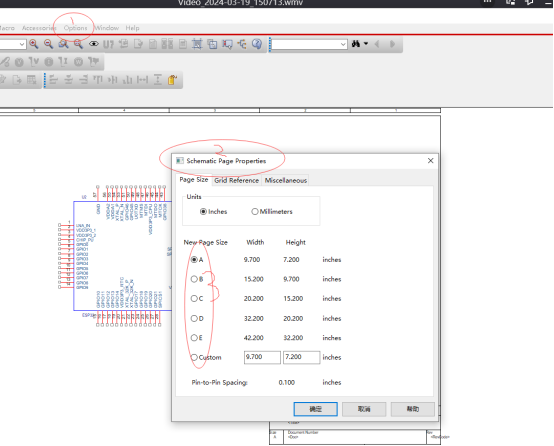

(2.3.2) 图纸大小的设置 在最上方的菜单栏 Options 中的 Schematic Page 再选择 ab c d 即可 a最小

(2.4)实操 放元器件的前提 就是要有自己的库(后缀名.OLB)

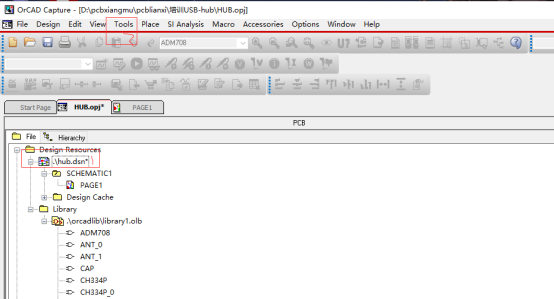

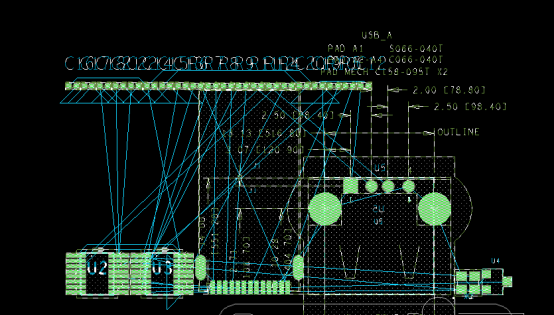

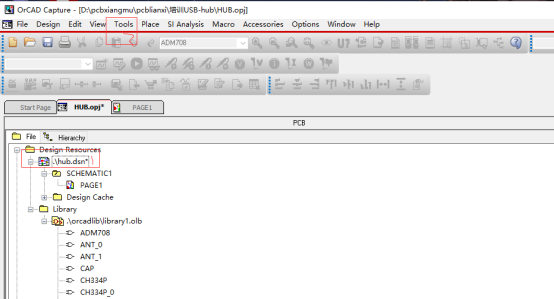

直接找到对应的文件夹D:\pcbxiangmu\pcblianxi\培训USB-hub 打开HUB.opj文件

1.导出网表

首先 选择page页面的最上方.\文件夹 然后 找到 菜单栏中的tools

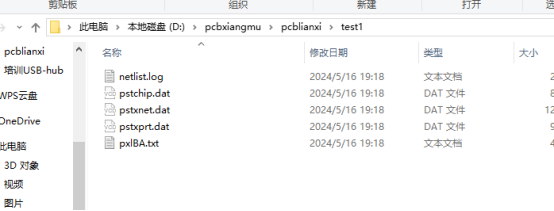

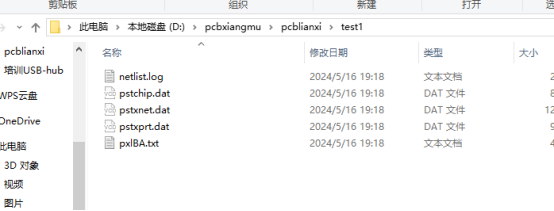

第一个create netlist 然后选择自己的路径 确认即可

2.导入网表 (在pcb封装软件中操作)

首先进入pcb封装软件中 随便选择前两个选项 (默认会打开上次使用的项目)

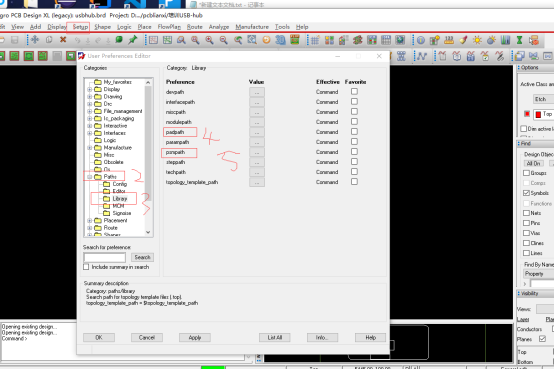

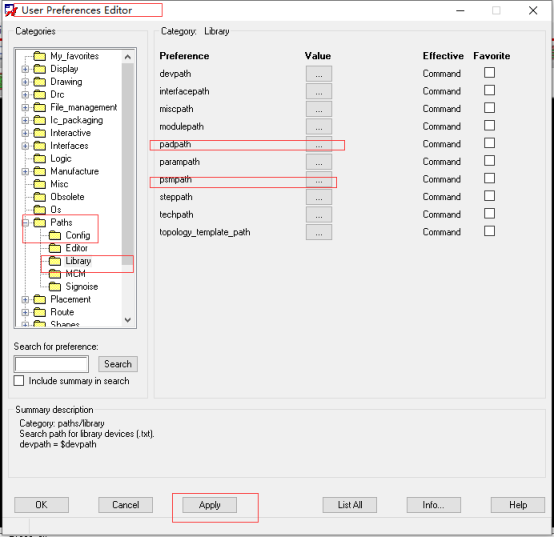

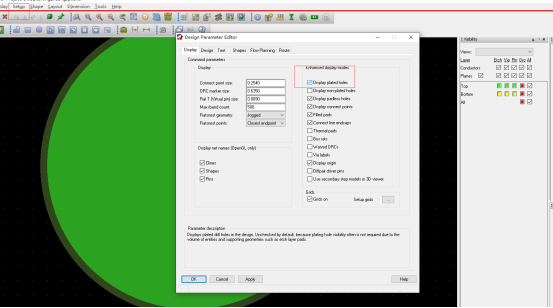

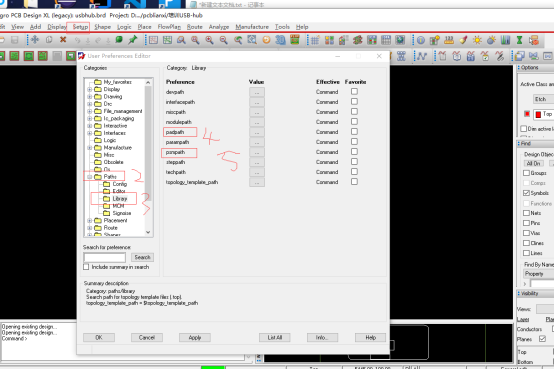

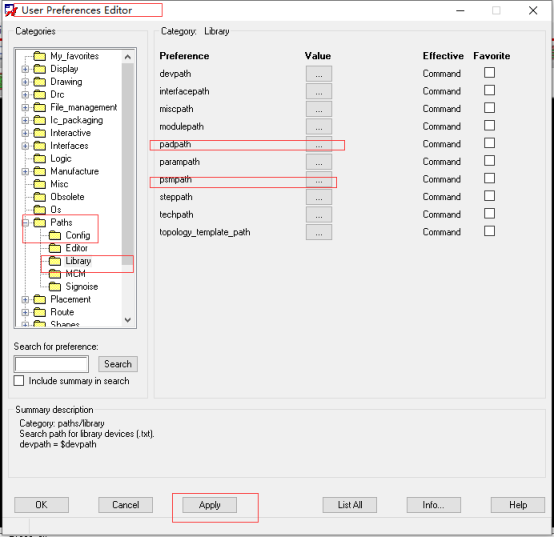

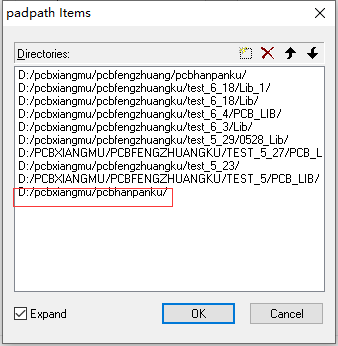

然后修改 默认的库文件 找到菜单栏中的 setup 选择最后一个文件 user 找到paths Library 修改padpath psmpath中的路径(修改为库的路径 —-焊盘库)

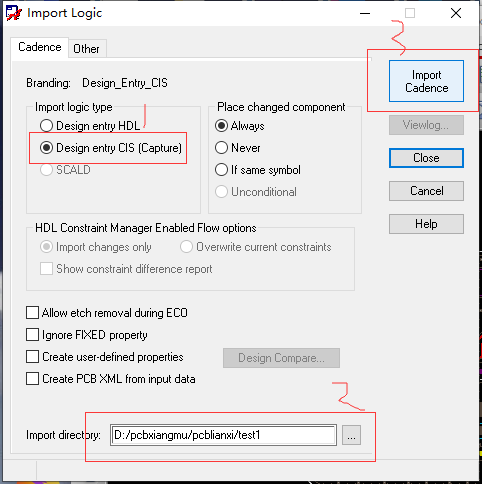

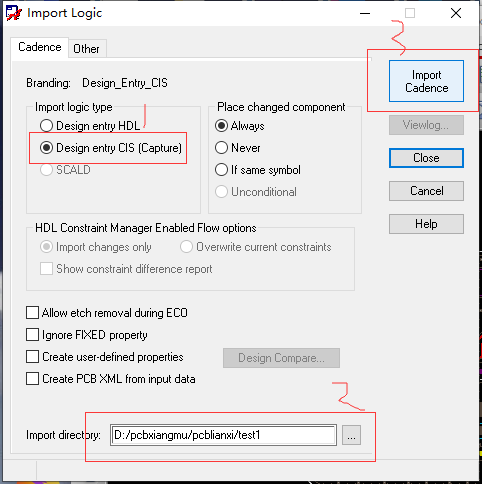

然后选择ok file import Logic 勾选CIS 最下面路径是自己的导出网表路径 最后选择右上角的import(不报错)即可

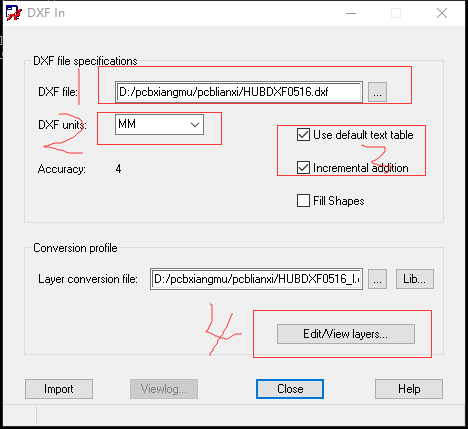

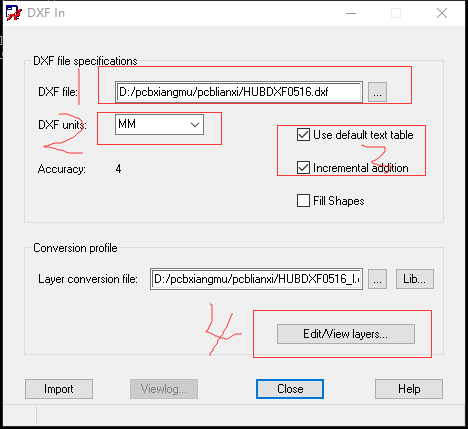

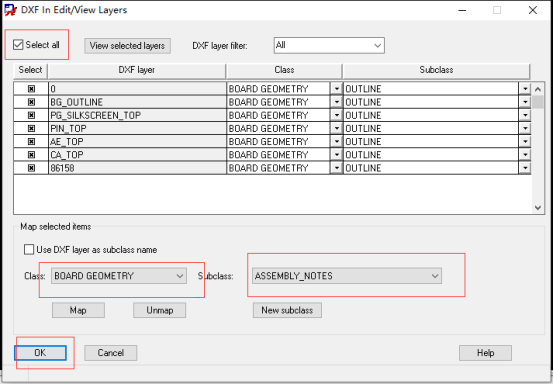

3.先导入dxf 首先 file import dxf 找到dxf文件 修改为mm 选择右边前两个框 然后点击Edit

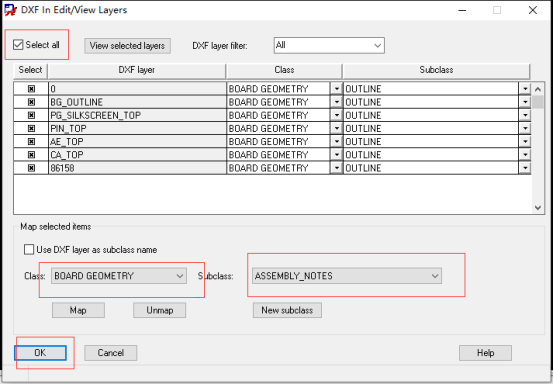

选择select all 左边选择第一个 右边选择倒数第三个 map 然后ok 导入即可

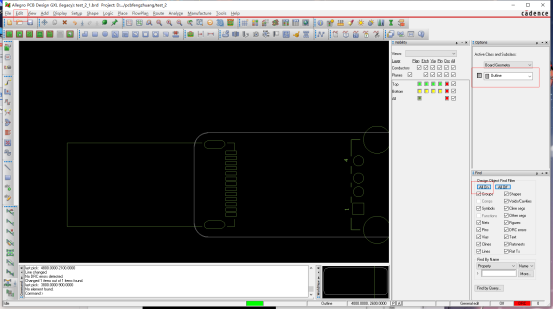

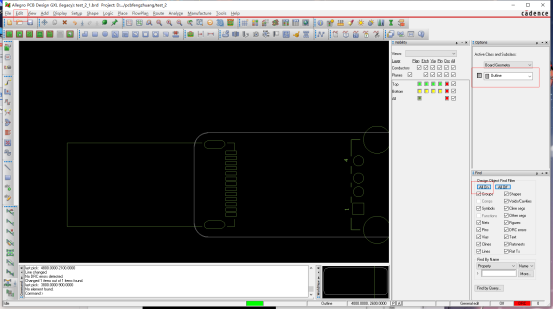

移动图形 直接框住 然后鼠标左键移动

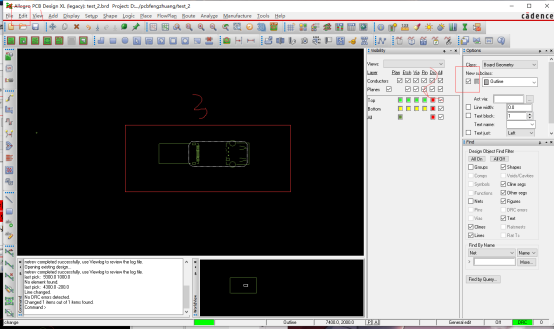

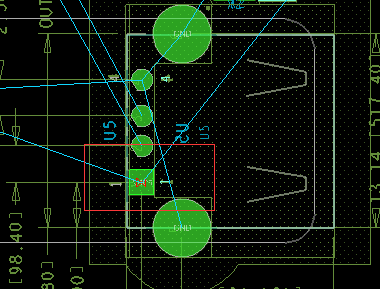

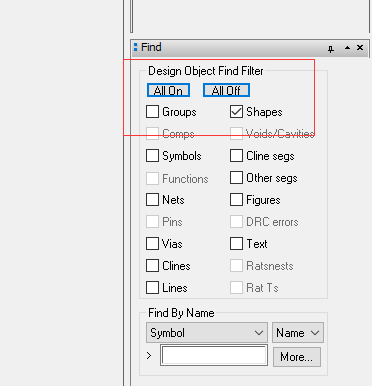

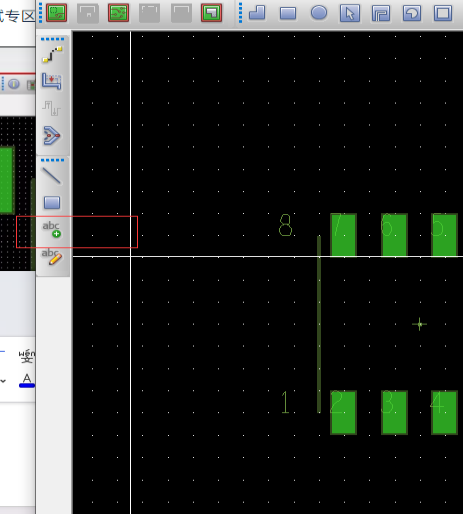

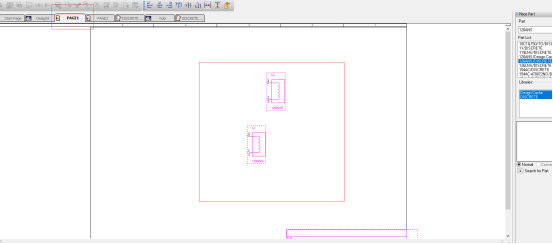

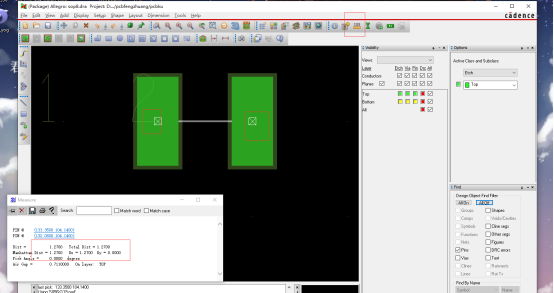

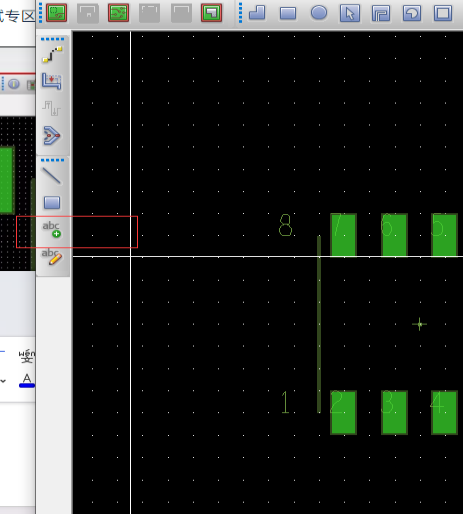

4. 放置器件 (先导网表) —一般情况不需要自己创建

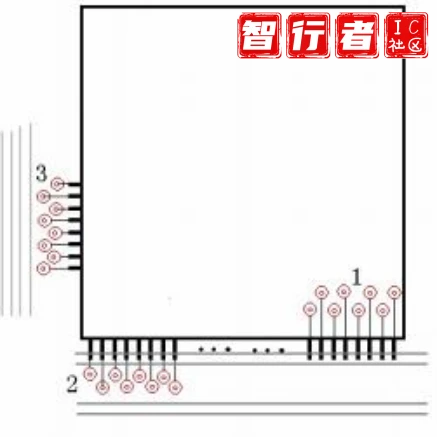

4.1 添加板框 【要有白色的框子】

(方法一)

Outline 前面是灰色的 All on

(方法二)

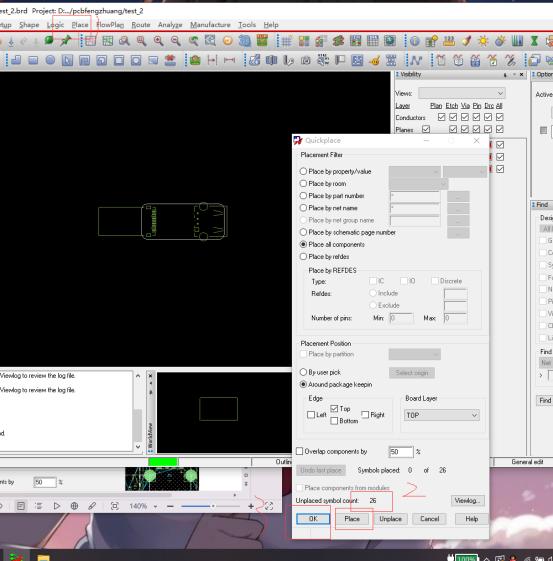

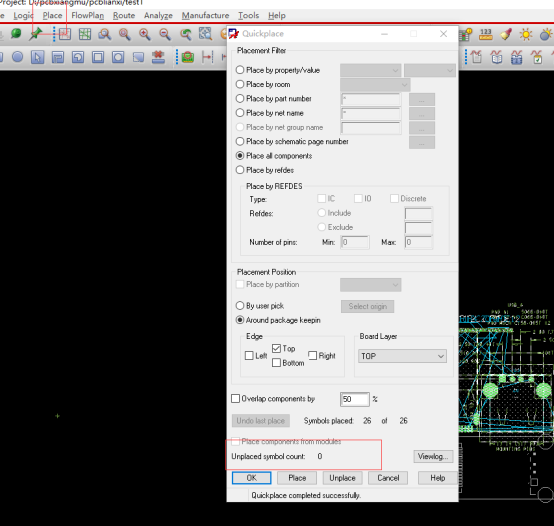

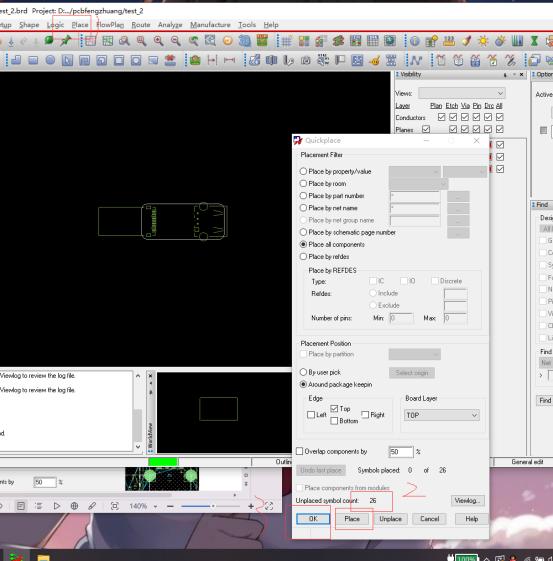

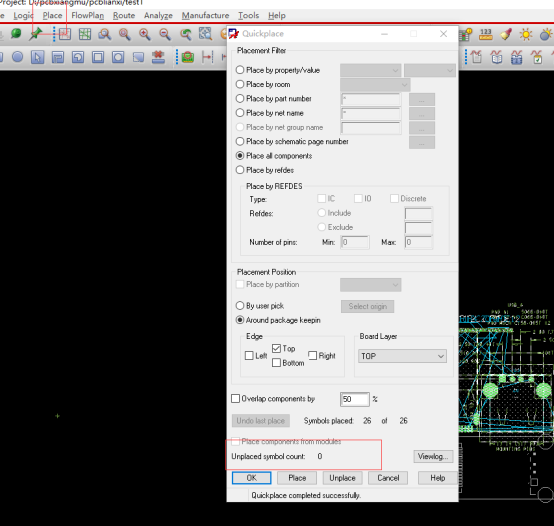

找到edit change 勾选右上角的outline 然后点击place 选择Qucik查看

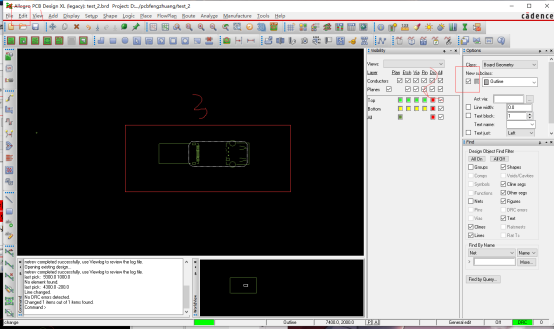

若count不是0 则直接点击place 再点击ok 即可放置元器件

(若count为0 则)Add line 鼠标左键划线 绘图即可 然后 place能弹出东西

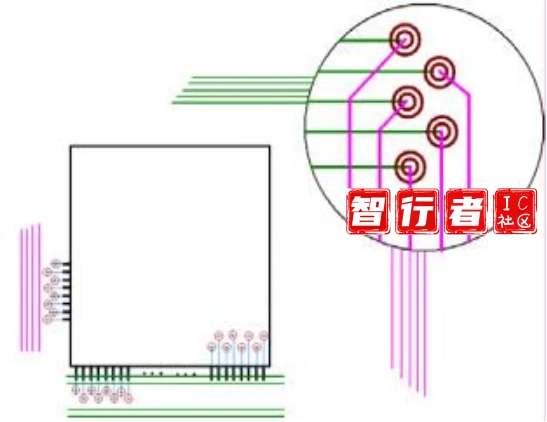

首先找到菜单栏中的 place 然后选择第二个 quickplace (没东西 则说明没有板框) 此时就可以查看元器件个数 然后点击最下面的 place 成功放置器件

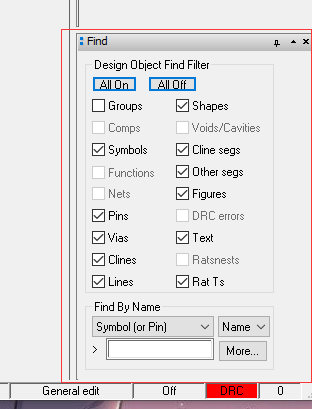

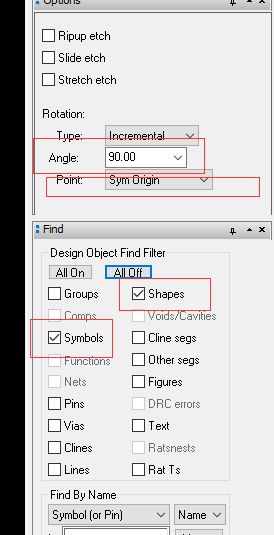

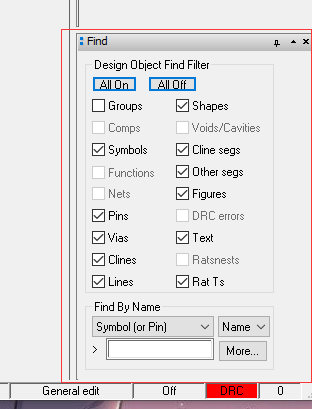

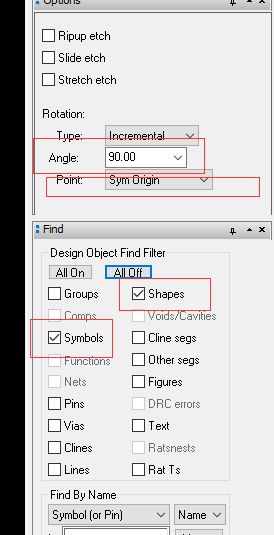

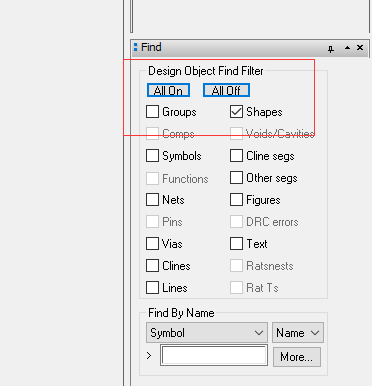

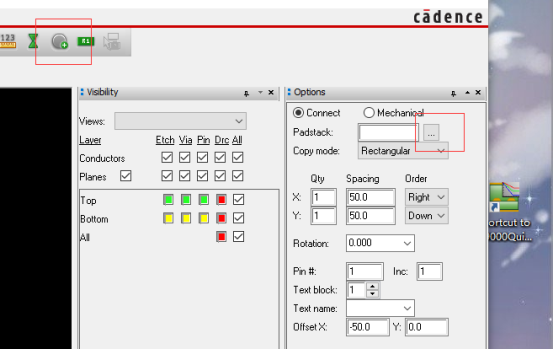

4.2. 【移动时一定要看属性 symbols】

5.然后进行移动

先点击移动 菜单栏中的十字架 或者 edit中的move 然后 选中原理图中的元器件 然后再pcb封装软件中 的移动 操作

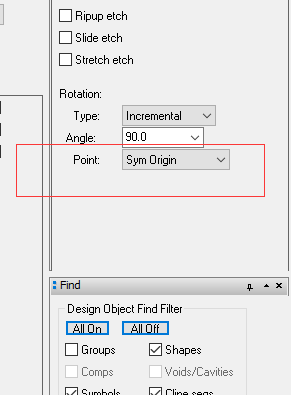

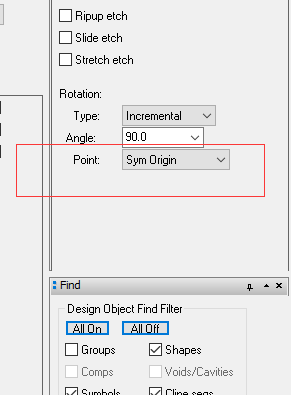

【移动不了时 查看options设置中的问题】

5.1. 当元器件可以移动时

右键 选择route 实现旋转

Done 固定位置

右边菜单栏中的 Angle是旋转度数 【移动一般只勾选Symbols Shapes】

一般移动使用Sym Origin

整体中心移动 body center

User pink 自定义的点(随机点) 不建议

Sym pin# pin脚标移动

5.2. 元器件定位 旋转过后即可单机取消

特殊情况

Pin 到pin

移动抓pin脚 任意pin脚

然后 将器件放在 对应的板框中 右键 选择最后一个 再点击pin 锁死 然后 再删除 shape即可

上铜 选择shape 倒数第三个 点击对应的的 引脚框 (然后使用绿色标识) done

然后移动 元器件到对应的位置上 再选中引脚 【若已经选择center 则直接左键单机 再down 删铜即可】 右键 放在对应的位置 done 选择最后一个 切换 数第一个 然后选择 shape center 最后再删铜即可(删铜要注意细节)

—没有删铜 会出现红色叉叉 然后只选择当前上铜区域删除即可

删铜 选中shapes

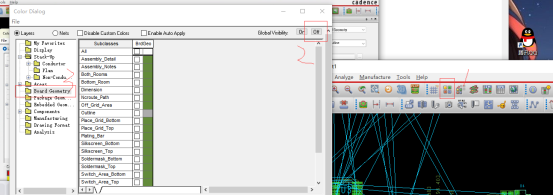

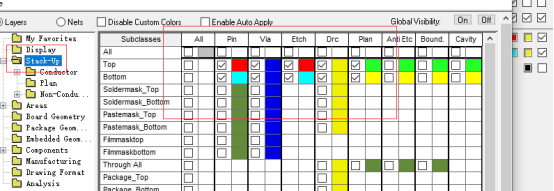

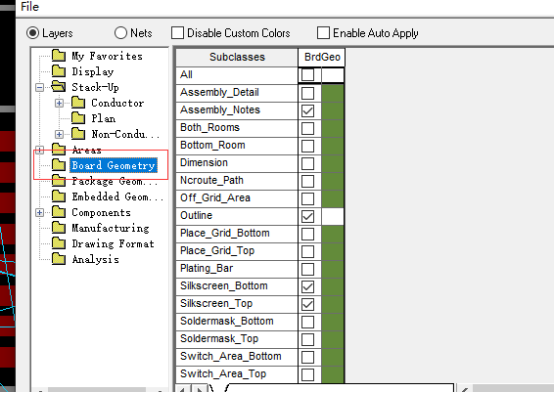

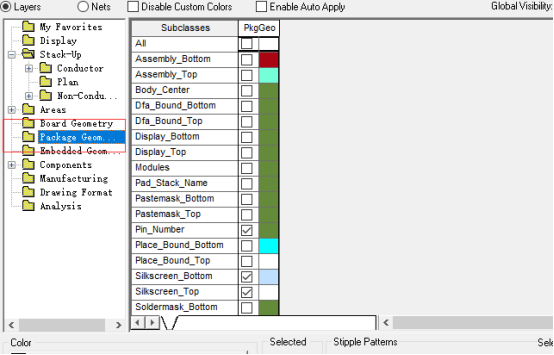

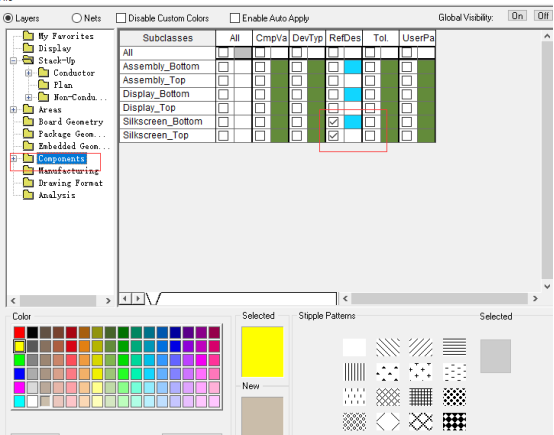

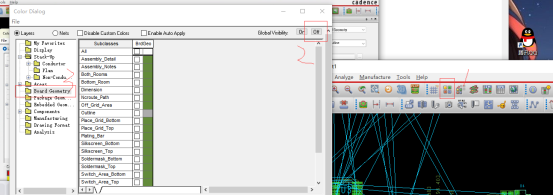

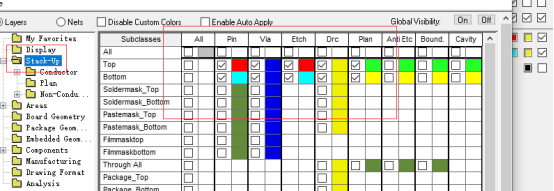

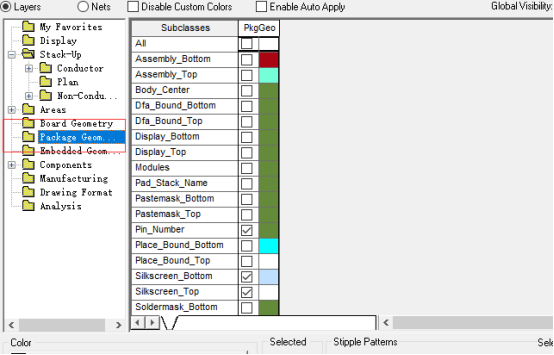

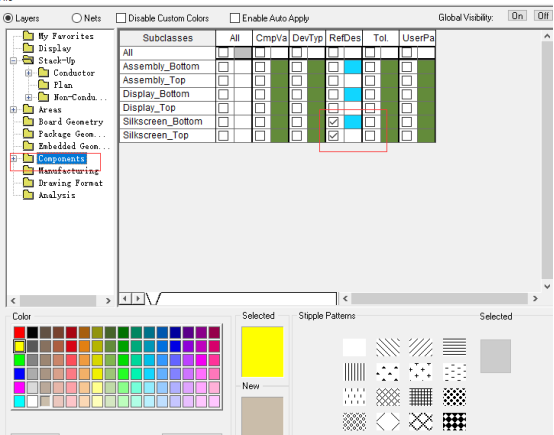

5.3.默认设置 选中菜单栏中的cloor192 选择右上角的off 将对钩全叉掉

然后选择对应的提示颜色

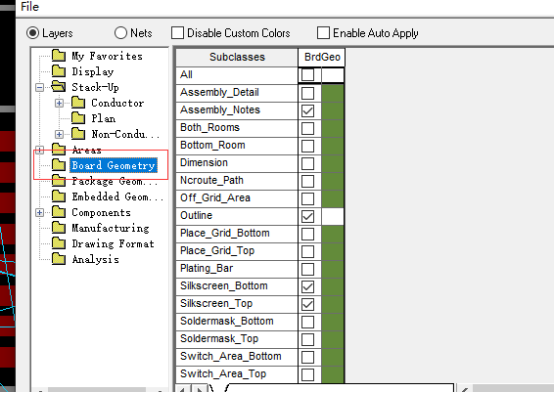

Board Geometry 选择Outline 板图 Ass Notes 定位 然后apply一下

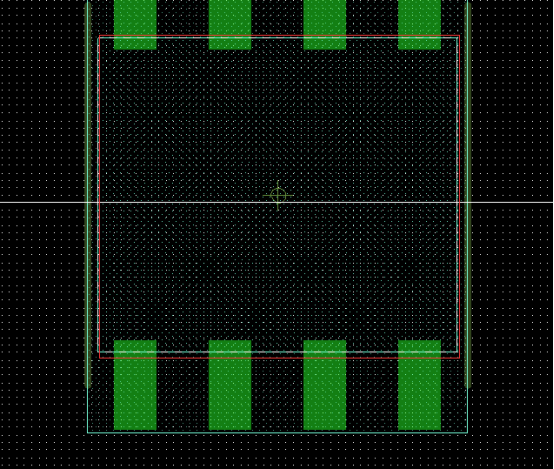

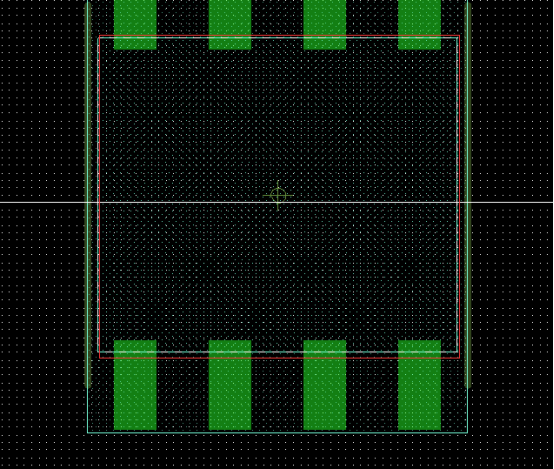

Package Geometry 选择Place_Bound_Bottom Top

Components 选择RefDes

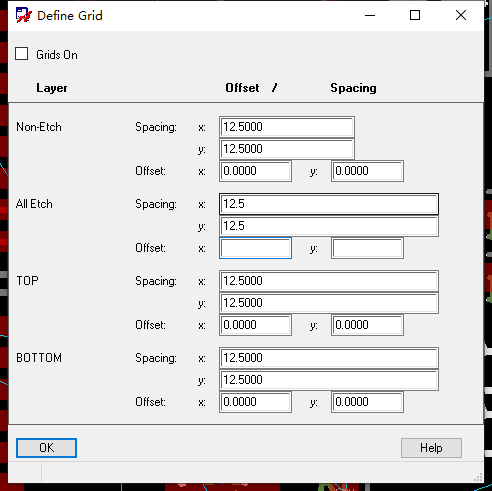

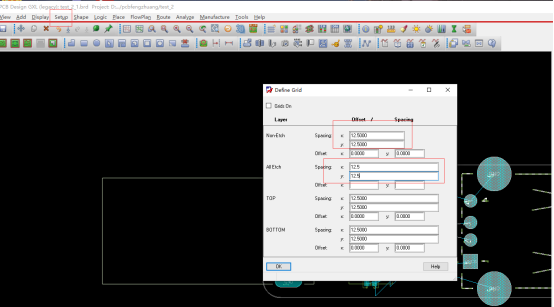

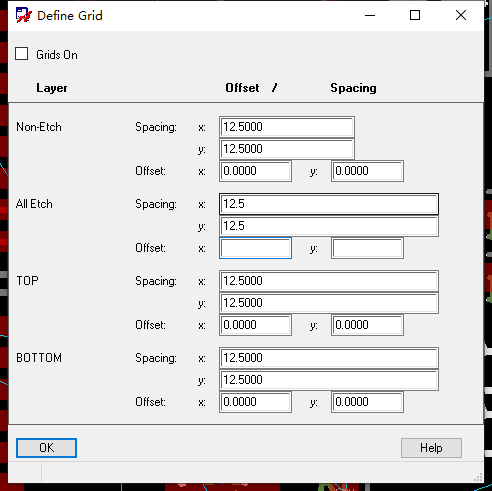

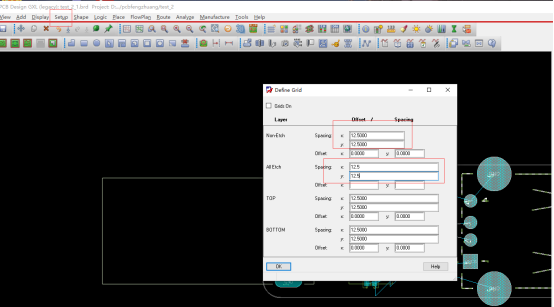

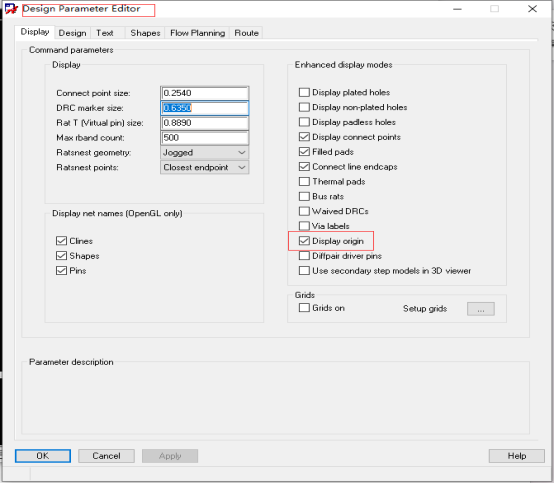

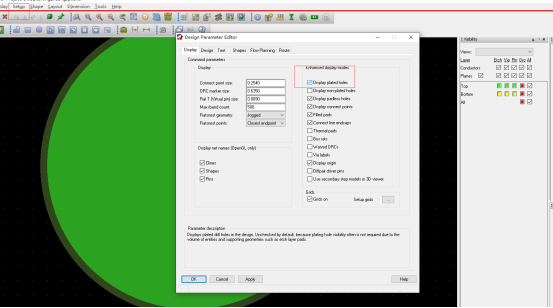

5.4 修改格点 12.5 25 set up Grids

5.5. 修改双击 打孔

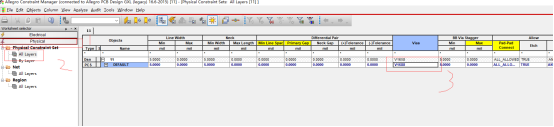

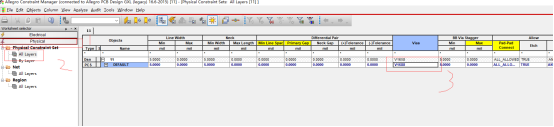

先点击 菜单栏 CM

然后 修改参数

打孔 在铺线的基础上 然后再双击

若没有 则将 v16x8.pad文件 放在对应的pcb封装库中

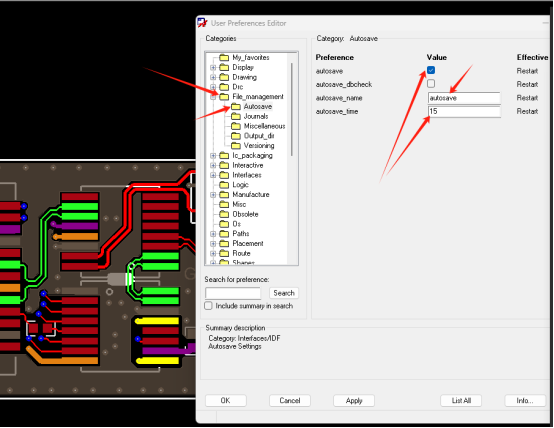

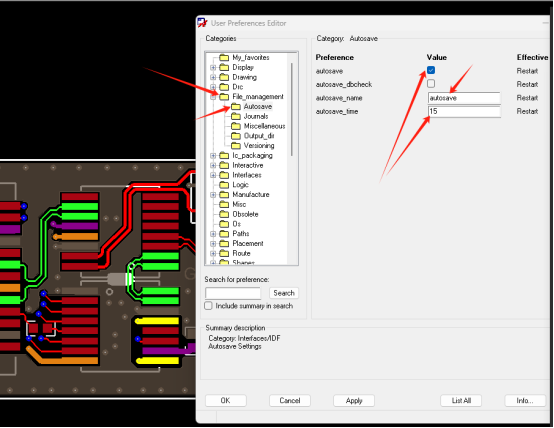

5.6.修改默认保存位置

Set up user

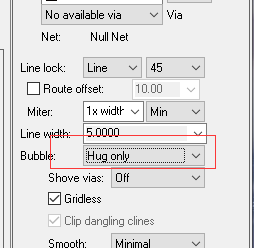

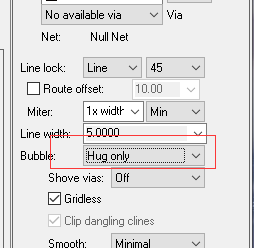

5.7. 走线 F9 建议使用hug only

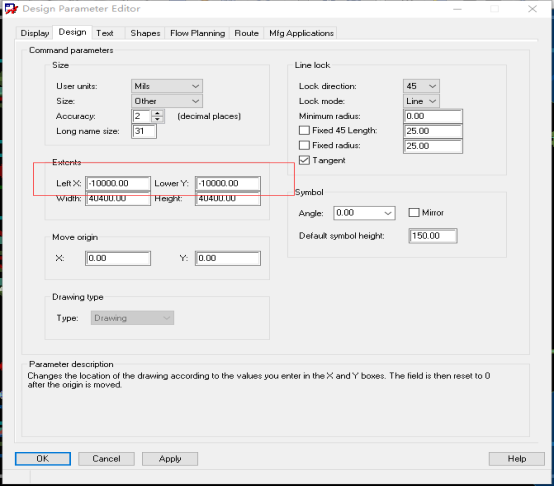

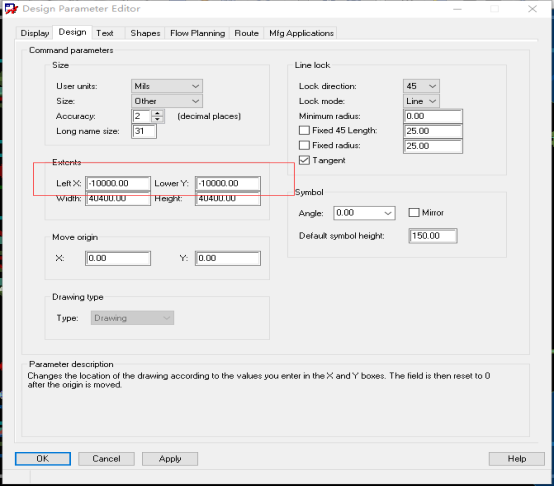

5.8.修改dxf文件的默认位置 (居中)

Set up 第一个 选择design 修改参数

5.17 第三天

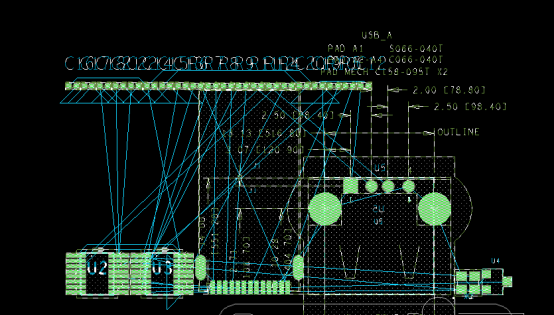

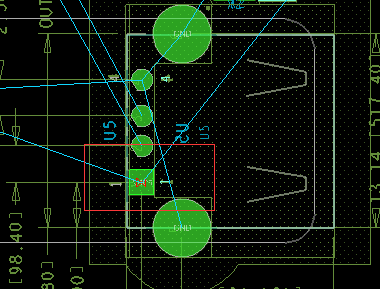

1.先将相关联的原理图器件放在一起 根据指定的dxf 文件 将导入的元器件放在对应的位置上

2.当使用 旋转快捷键时 要双击

3. 实操

3.2.pcb封装图 放置元器件 连线

–导入网表 dxf文件 mirror 双击过后 再确定

–修改网格 12.5 6.25 可以相切 菜单栏 set up grids

–若打孔的位置 直接在元器件上 则 先打开走线 F9 然后 选择最后一个 第一个选择 off

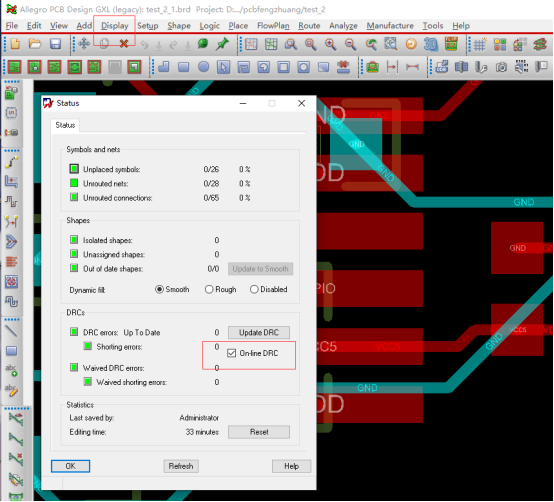

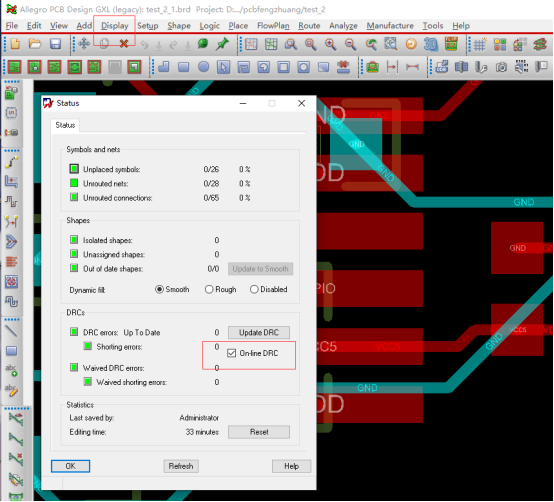

–当连接完成后 可以在 菜单栏中的display中进行查看

–报黄 红 都是有问题的

[ceo-payment-hide sku=”200″]

3.1.画原理图

1.先创建新的design

然后导入pcb原理图库 【导入老师的原理图库】 选中元器件 roate进行旋转  然后修改页面大小 在菜单栏的options中 选择schematic page 【a最小】 –双击放置器件 右键 End modle取消 –框选器件 然后可以移动 –GND 地线

然后修改页面大小 在菜单栏的options中 选择schematic page 【a最小】 –双击放置器件 右键 End modle取消 –框选器件 然后可以移动 –GND 地线  –VCC5电源 –连线

–VCC5电源 –连线  快捷建 W esc直接取消连线操作 –没有连上的线 则表示该引脚未使用 –写字 标注 然后移动到对应的位置上 快捷建 N (只能放在自己画的黑线上)

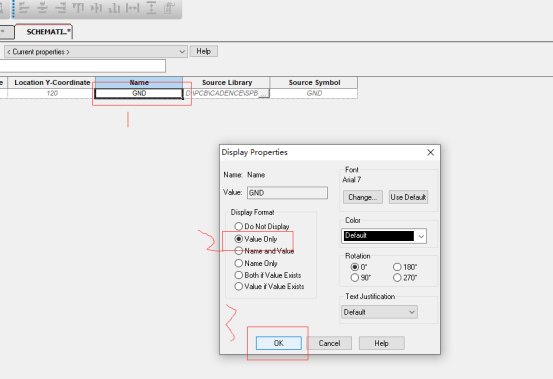

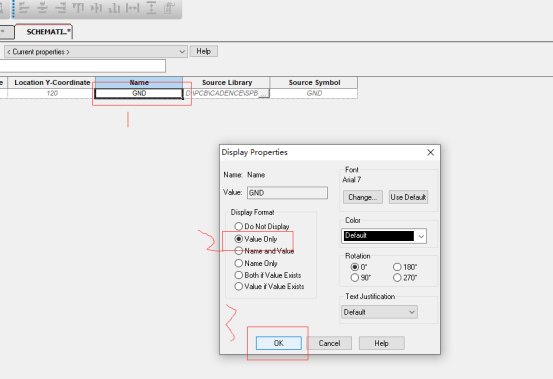

快捷建 W esc直接取消连线操作 –没有连上的线 则表示该引脚未使用 –写字 标注 然后移动到对应的位置上 快捷建 N (只能放在自己画的黑线上)  –显示 GND 双击GND图标 然后修改默认显示 保存关闭即可

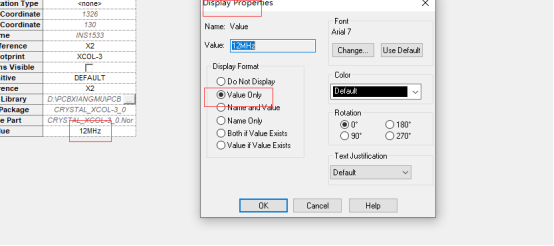

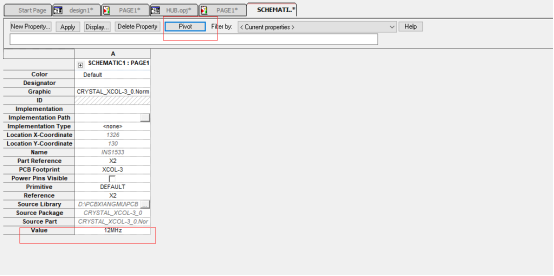

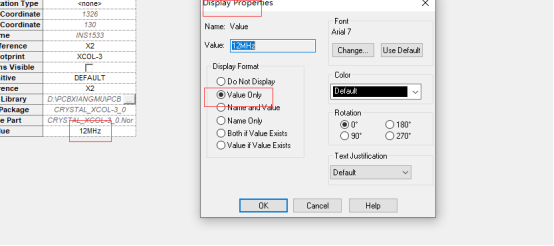

–显示 GND 双击GND图标 然后修改默认显示 保存关闭即可  –显示晶振的默认值 双击 晶振元器件

–显示晶振的默认值 双击 晶振元器件  若未显示 则右键 当前晶振数值 display 选择Value only 保存即可

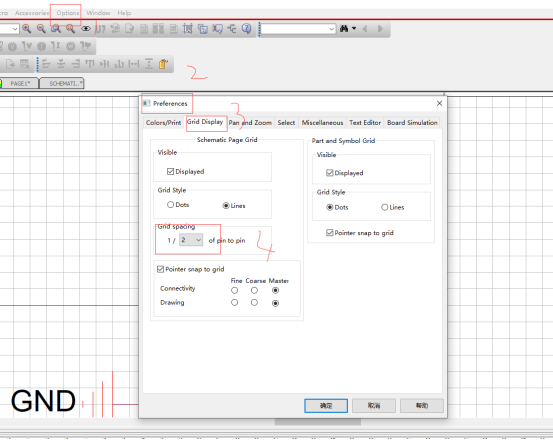

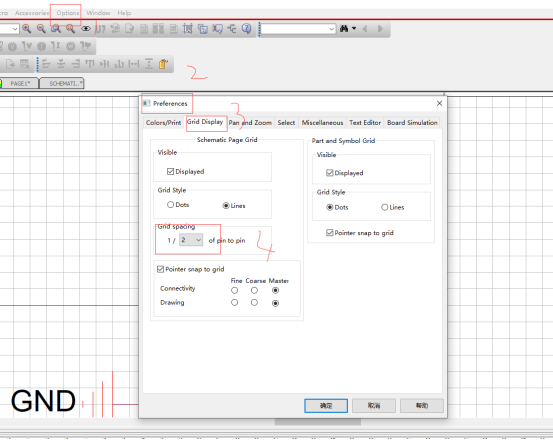

若未显示 则右键 当前晶振数值 display 选择Value only 保存即可  –修改格点

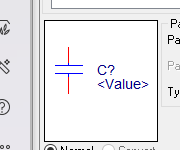

–修改格点  –然后选择对应的组件 电阻RES_0 — 当原理图完成后 然后进行 导出网表 操作 –注意 判断是否连接上 可以将先拖动一下 若一起移动则连接成功

–然后选择对应的组件 电阻RES_0 — 当原理图完成后 然后进行 导出网表 操作 –注意 判断是否连接上 可以将先拖动一下 若一起移动则连接成功

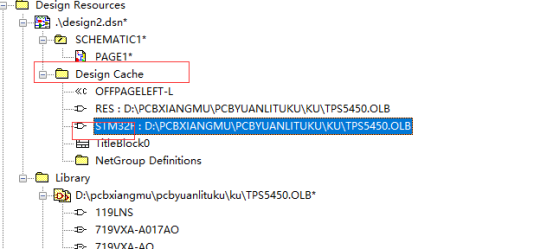

2.所有的元器件 的封装 [切记所有的封装和值都要保持一致]

value PCB Footprint 都要跟老师的模板保持一致 –【切记 不然导不出网表】 J1 pcb footprint usb-tf value值 USB2.0 AM & MICRO SD U2 SOP16_P0635 CH334R C21 C0402 5.6pF C22 C0402 5.6pF C17 C0402 0.1uF C18 C0402 10uF X2 2520 12MHz U3 SOP16_P0635 GL823K R6 R0402 36 R5 R0402 36 R10 R0402 36 R9 R0402 36 R8 R0402 36 R7 R0402 36 R4 R0402 4.7K C13 C0402 4.7uF C14 C0402 0.1uF/NC C15 C0402 4.7uF C16 C0402 2.2uF U4 SOT23 SSP7615-33MR C19 C0402 1uF C20 C0402 1uF U5 usb_a usb_a R11 R0402 0R R12 R0402 0R C12 c0402 1uF

4. 当我们导入网表 成功时 此时进行pcb封装的先关操作

3.1. 导入网表 首先创建一个新的 pcb封装文件 修改默认设置 导入dxf文件的位置 color192的设置 打孔大小 修改格点12.5 修改默认的库文件 setnup users 里面的 path library padpath psmpath (pcb封装库的位置) 然后导入 file import login (选择网表的位置) 然后导入对应的dxf 文件 并修改其默认配置 然后 画板框 移动对应的器件 change place 3.2.然后开始放置器件和走线 打孔 先移动 J1 U5 选择shape center 和 off 开始按照原理图 进行pcb封装图的走线 和 打孔(顶层到底层已经连通了 故既可以走正面也可以走背面) 器件还可以放在背面(在移动的基础上) Display show rats net 显示部分网络 镜像只能一个器件一个器件的镜像 走线 要么走正面 要么走反面 【注意 制作pcb封装图时 一定要一块一块的去处理 然后再进行拼接】

5.20 第四天

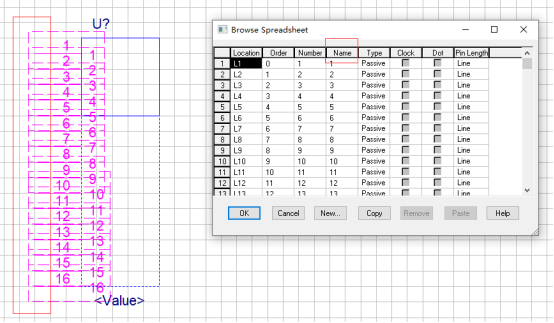

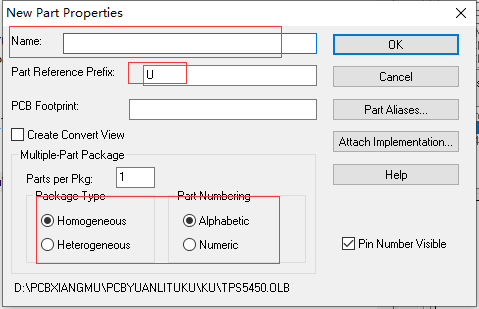

(1)绘制原理图库

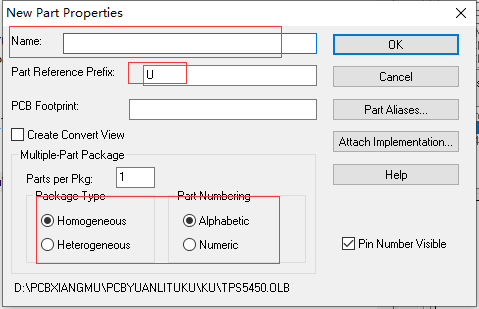

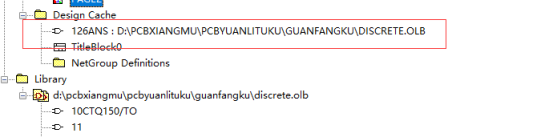

先右键LIbrary文件夹 然后 add file 添加对应的pcb原理图库文件  然后 选中当前的pcb原理图库文件 右键 new part

然后 选中当前的pcb原理图库文件 右键 new part  名字 U类型 下面两个 左边是分割

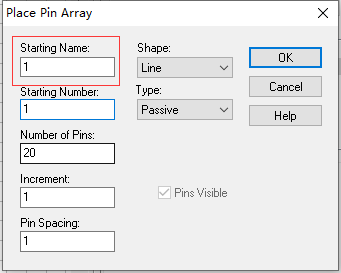

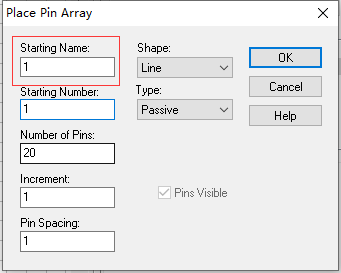

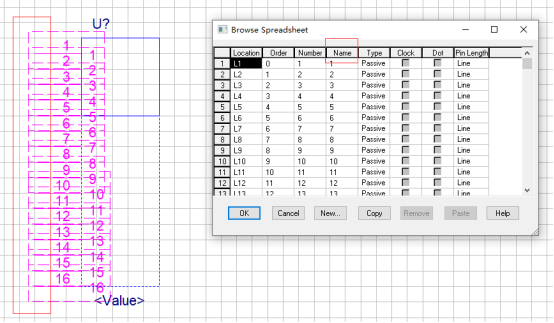

名字 U类型 下面两个 左边是分割  注意一定要给元器件 留有足够的空间 不然会叠在一起 一般绘制过程 —-不需要考虑绘制的pcb原理图有多大 第一个 画pin脚标识 第二个和第三个 是用来 改变封装大小的 第四个 快速添加序号用的

注意一定要给元器件 留有足够的空间 不然会叠在一起 一般绘制过程 —-不需要考虑绘制的pcb原理图有多大 第一个 画pin脚标识 第二个和第三个 是用来 改变封装大小的 第四个 快速添加序号用的  当画成矩形的时候 直接可以移动大小

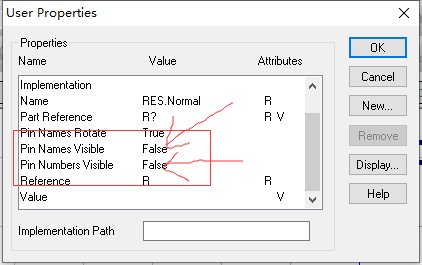

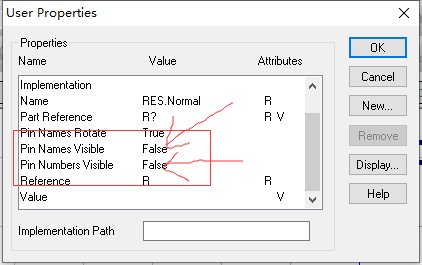

当画成矩形的时候 直接可以移动大小  Pcb原理图 双击空白处 即是元器件 修改属性为false 电阻 顶层

Pcb原理图 双击空白处 即是元器件 修改属性为false 电阻 顶层  管脚很多 使用矩阵放置 选中多个引脚 右键 第一个 修改

管脚很多 使用矩阵放置 选中多个引脚 右键 第一个 修改  右键 库文件 add 选择 官放原理图 方库文件 【一般情况 直接使用公司的库文件】 右键别人的库里面的某个封装 copy 然后 选择自己的库路径 右键 paste

右键 库文件 add 选择 官放原理图 方库文件 【一般情况 直接使用公司的库文件】 右键别人的库里面的某个封装 copy 然后 选择自己的库路径 右键 paste

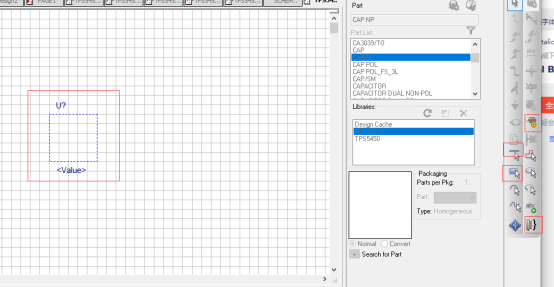

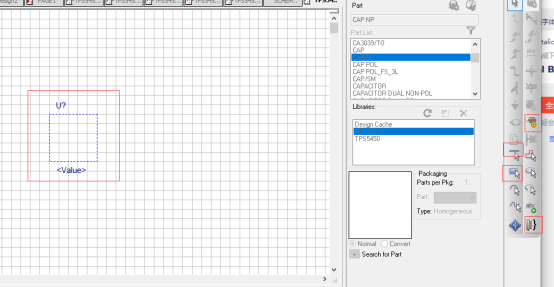

PLACE 连页符 off page 磁珠(类似于电阻) bead 当我们二次修改 pcb原理图时 就可以在design中右键 要更新的元器件 update一下 CAP 电源

PLACE 连页符 off page 磁珠(类似于电阻) bead 当我们二次修改 pcb原理图时 就可以在design中右键 要更新的元器件 update一下 CAP 电源  当我们绘制pcb的原理图时 desige Cache中才会显示内容

当我们绘制pcb的原理图时 desige Cache中才会显示内容

使用快速添加pin脚

使用快速添加pin脚  右键框选 然后编辑

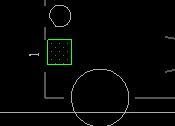

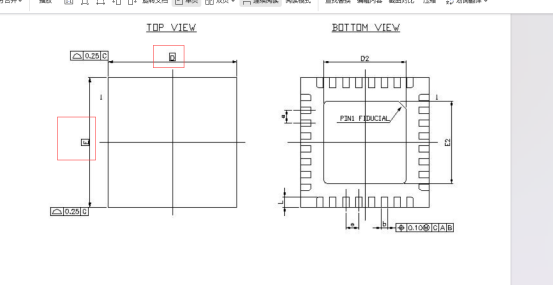

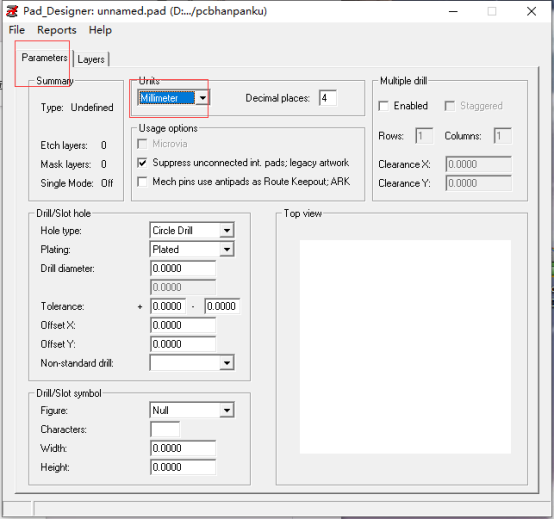

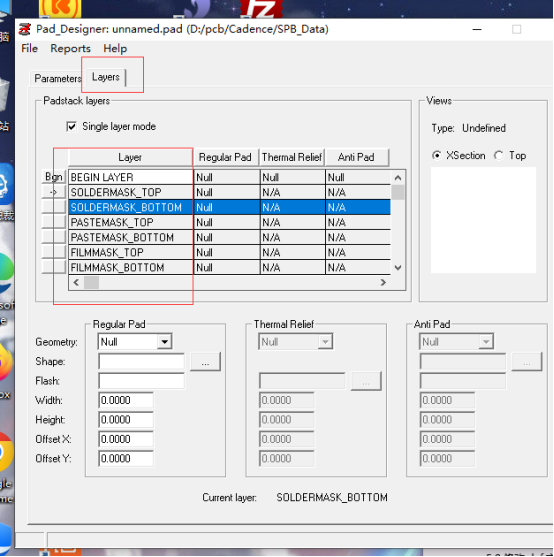

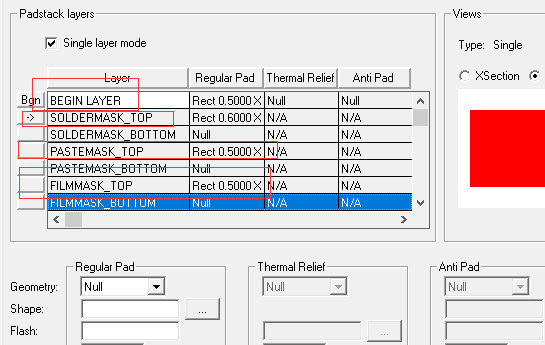

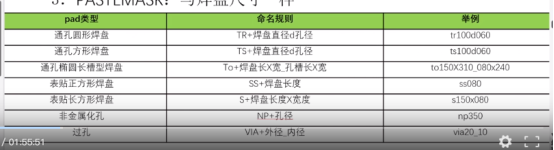

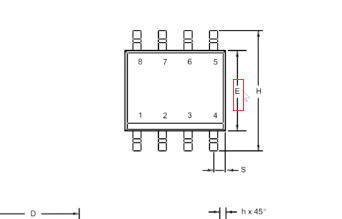

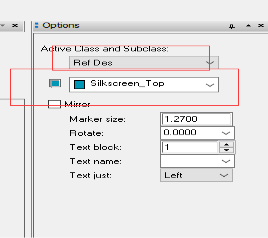

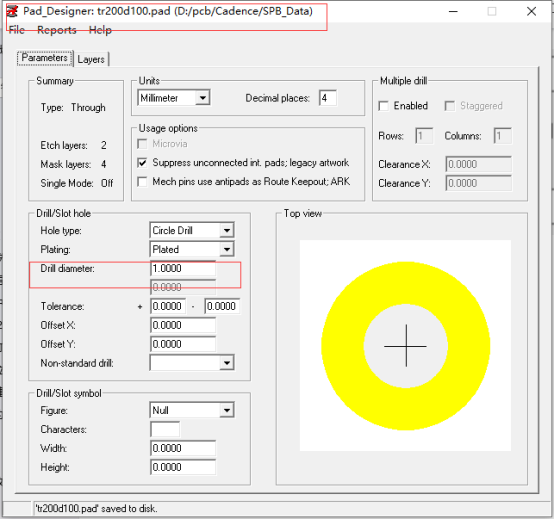

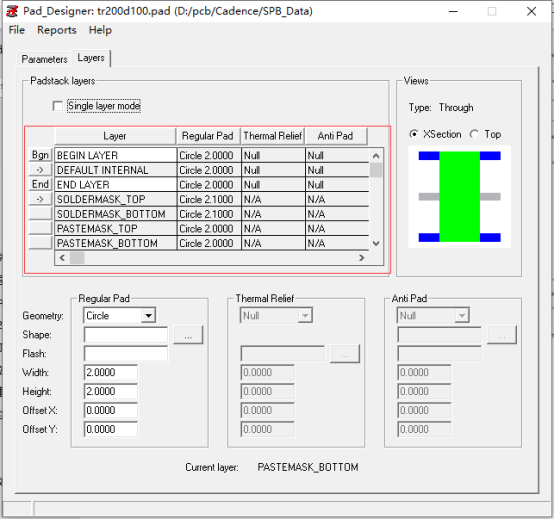

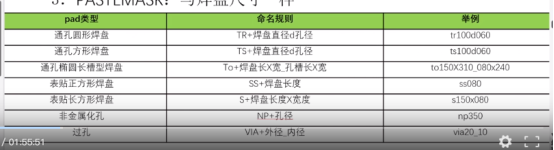

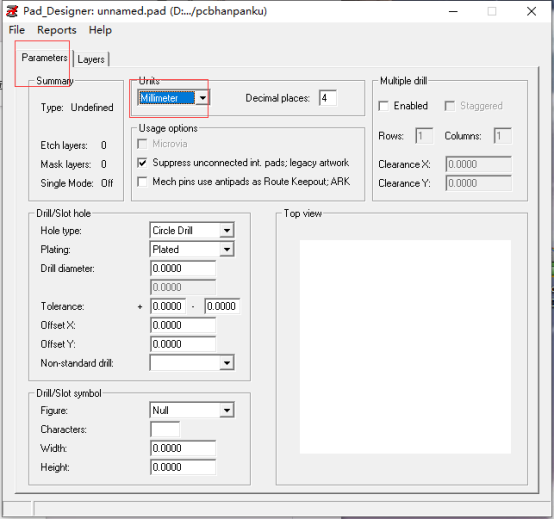

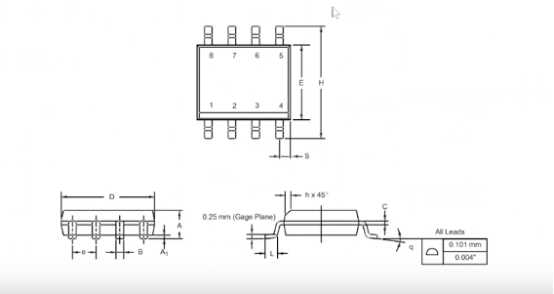

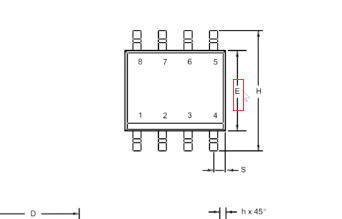

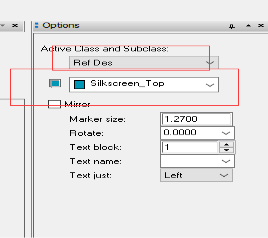

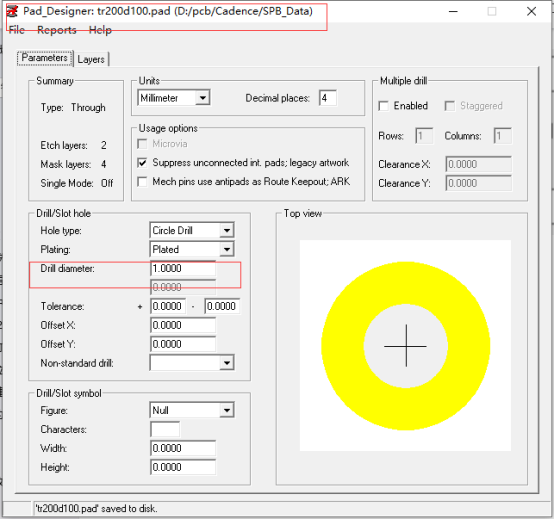

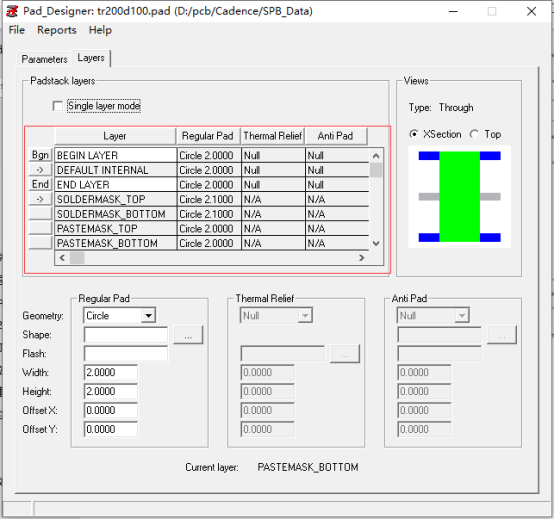

右键框选 然后编辑  Pcb的封装 必须严格要求 红色的 焊盘(PAD) 丝印框(silk) 专门画 焊盘 Pad_Designer 贴片 0 plated电镀 内壁普通 本体层 装配层 比器件 大一点 透视图 用虚线表示 D X E 钢网 焊盘库 长方形 (长* 宽) 汉字 REF DES

Pcb的封装 必须严格要求 红色的 焊盘(PAD) 丝印框(silk) 专门画 焊盘 Pad_Designer 贴片 0 plated电镀 内壁普通 本体层 装配层 比器件 大一点 透视图 用虚线表示 D X E 钢网 焊盘库 长方形 (长* 宽) 汉字 REF DES  1.焊盘的相关操作 先使用pad工具 绘制焊盘 修改单位为毫米

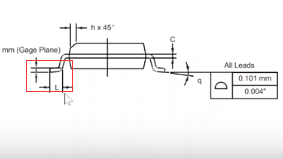

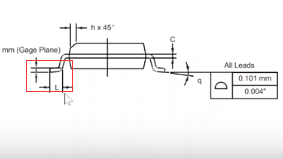

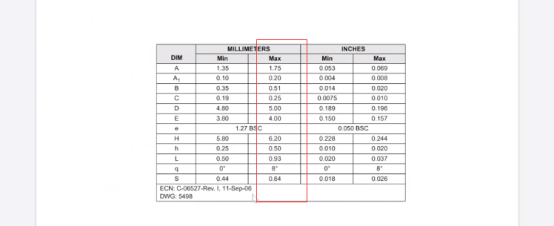

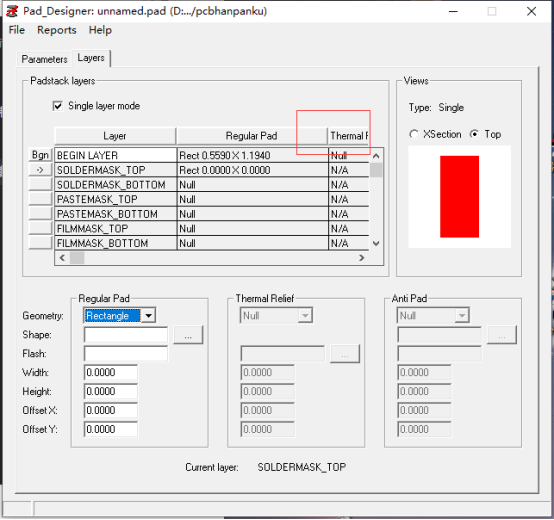

1.焊盘的相关操作 先使用pad工具 绘制焊盘 修改单位为毫米  参数:hole type 孔的类型 表贴焊盘 通孔焊盘 贴片的不用修改 single只有单层 不勾选则是含有多层 然后进行绘制焊盘的先关操作: 辨别是否是表贴器件还是通孔器件 看管脚是直的还是竖直的

参数:hole type 孔的类型 表贴焊盘 通孔焊盘 贴片的不用修改 single只有单层 不勾选则是含有多层 然后进行绘制焊盘的先关操作: 辨别是否是表贴器件还是通孔器件 看管脚是直的还是竖直的

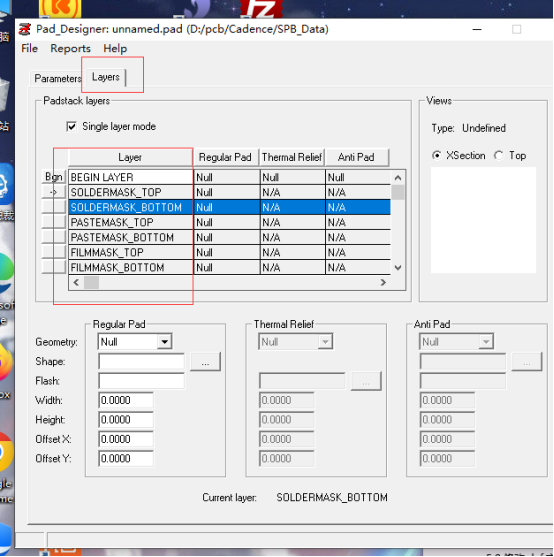

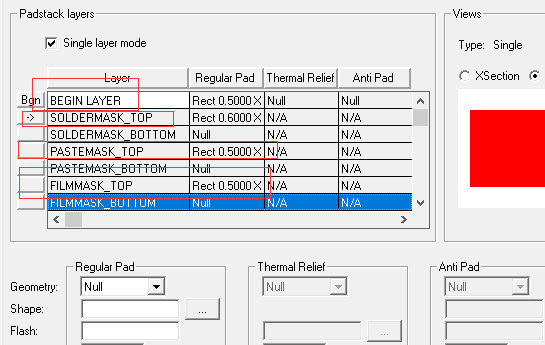

(2)绘制pcb焊盘库

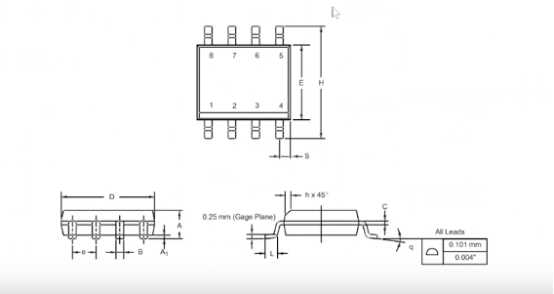

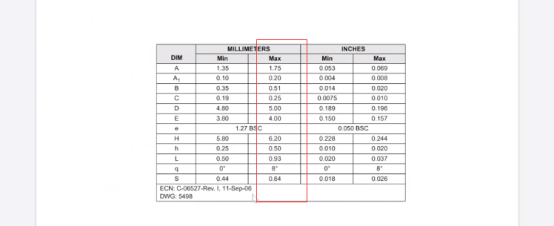

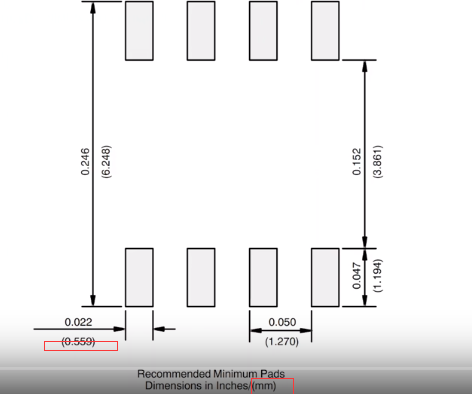

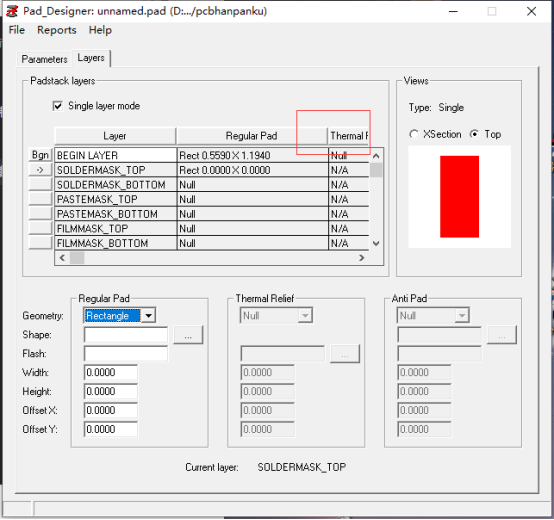

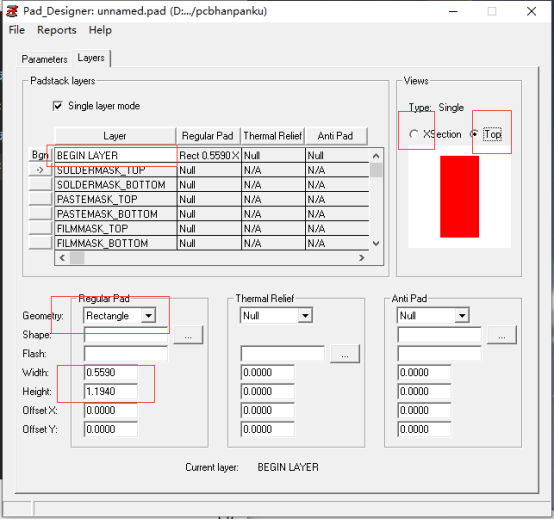

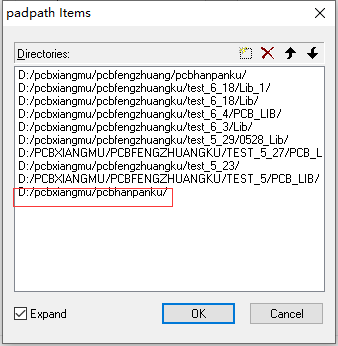

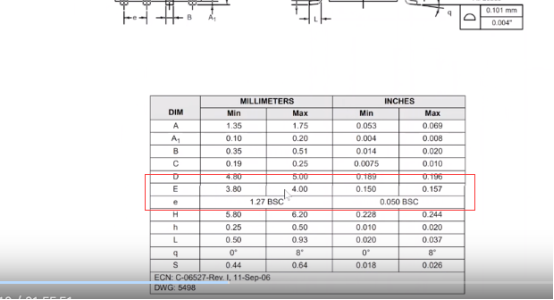

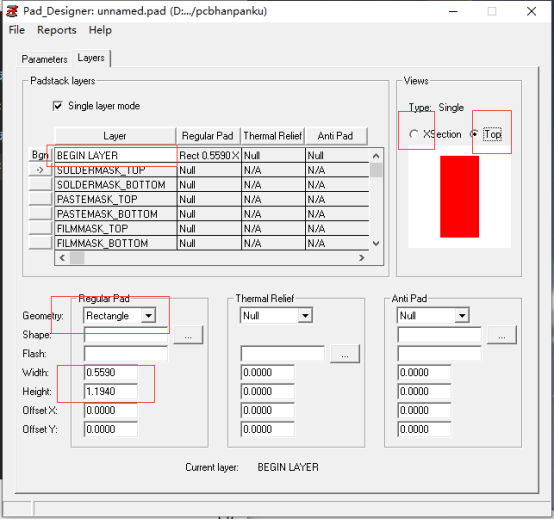

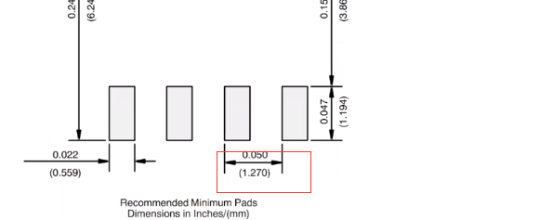

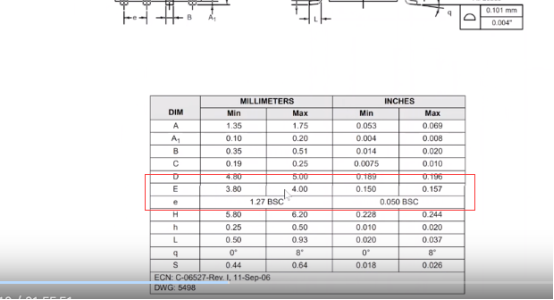

(2)绘制表贴焊盘 【画的是俯视图 顶层】 —-只修改top层即可 若是插件的 则bottom也要设置 不需要勾选single Single 表层 选择图形 Beg焊盘本体 solder开创(比焊盘大一圈 大0.1mm) paste 钢网(与焊盘大小保持一致) Beginlayrerr 焊盘的本体

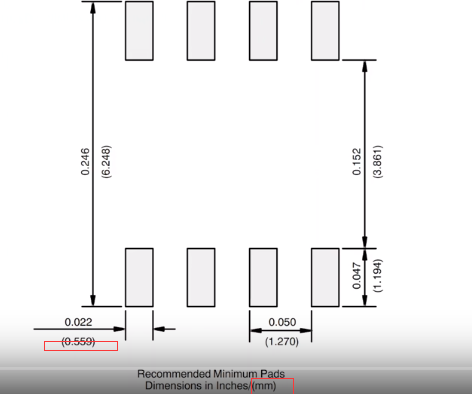

一般没有推荐尺寸时 使用最大值进行绘制pcb焊盘

一般没有推荐尺寸时 使用最大值进行绘制pcb焊盘

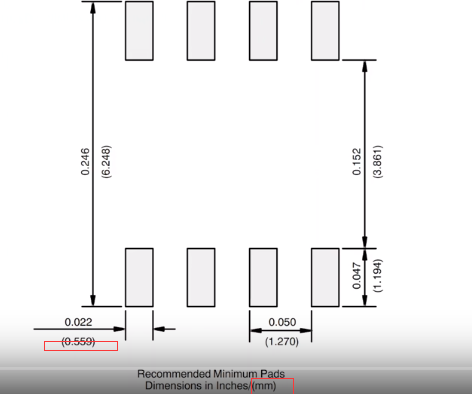

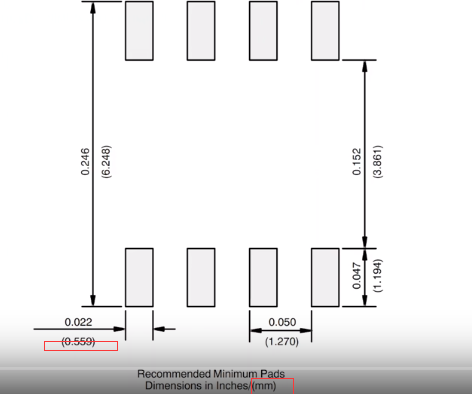

推荐的 可以在下面看到 括号中的是毫米单位

推荐的 可以在下面看到 括号中的是毫米单位  由此可见 宽 0.559 长1.194 然后 pad进行绘制 右上角 选择top 顶视图 x是横切面 Rect 矩形 可以拖动小方块 使其全展开

由此可见 宽 0.559 长1.194 然后 pad进行绘制 右上角 选择top 顶视图 x是横切面 Rect 矩形 可以拖动小方块 使其全展开

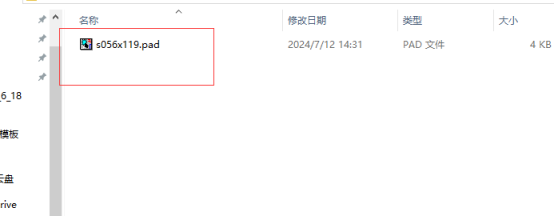

当创建完成后file save as 进行保存 命名规范

当创建完成后file save as 进行保存 命名规范

原来的尺寸是 0.559X1.1940 s是表贴矩形焊盘 使用四舍五入 取056就相当于0.56毫米 119=1.19 此时pcb焊盘做完以后 就可以进行绘制pcb封装库了

原来的尺寸是 0.559X1.1940 s是表贴矩形焊盘 使用四舍五入 取056就相当于0.56毫米 119=1.19 此时pcb焊盘做完以后 就可以进行绘制pcb封装库了

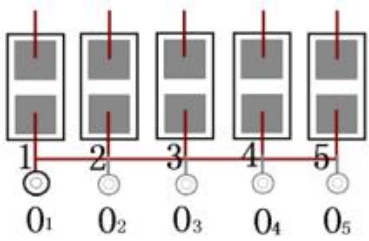

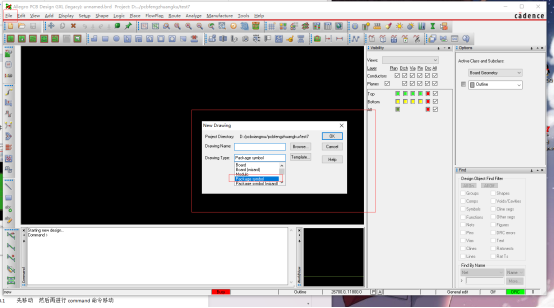

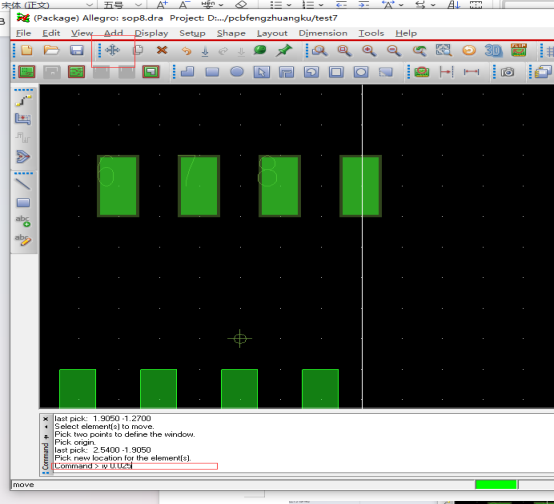

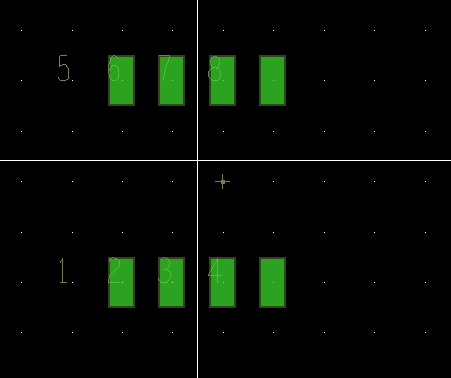

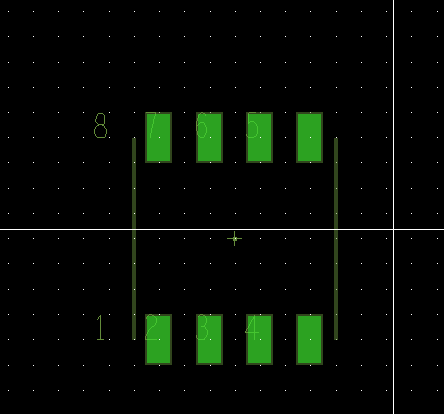

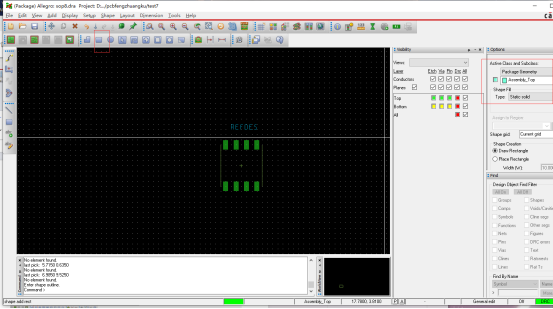

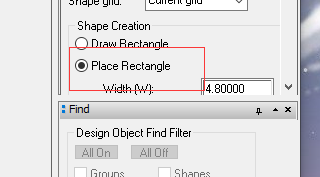

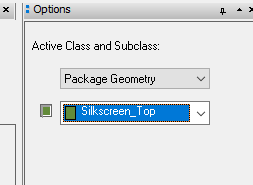

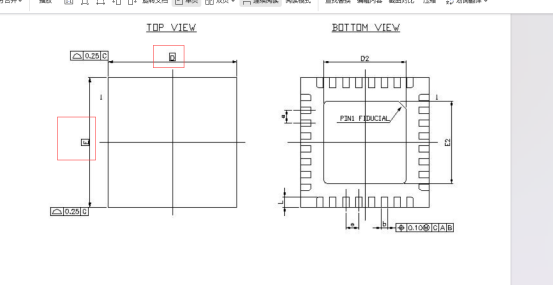

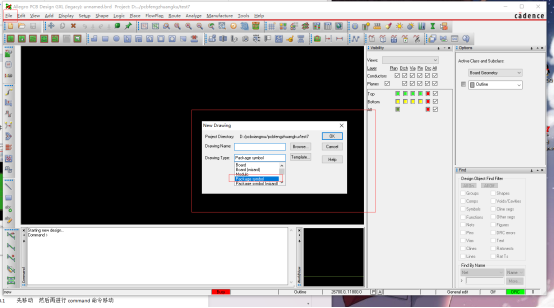

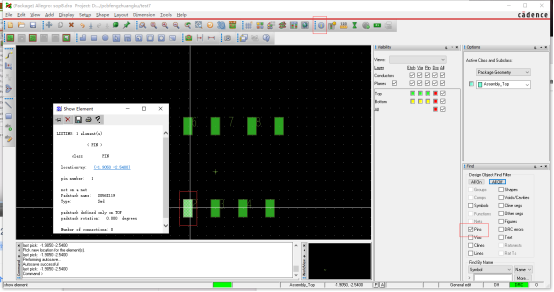

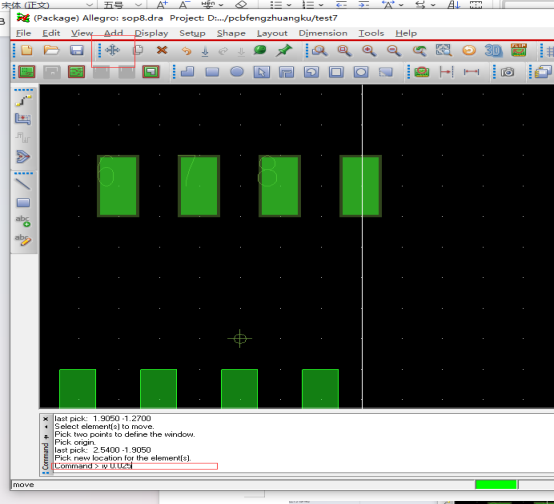

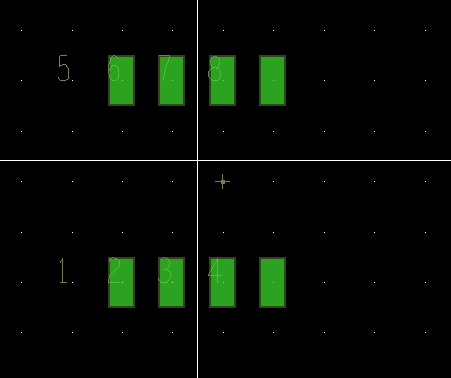

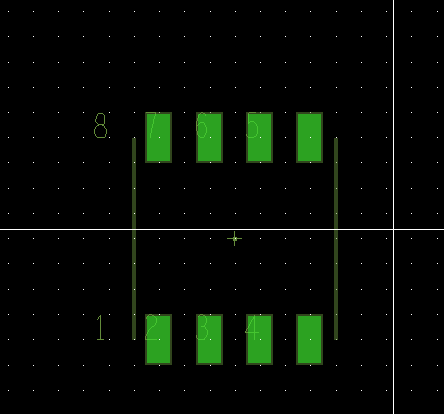

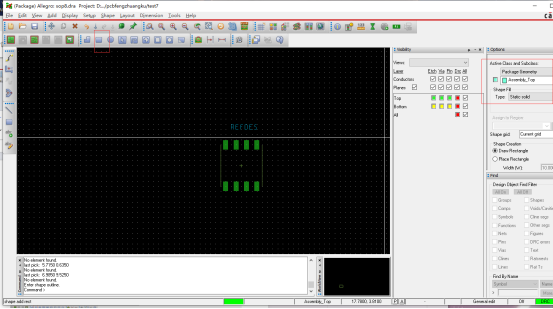

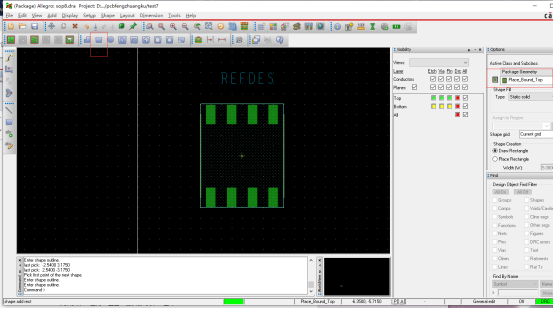

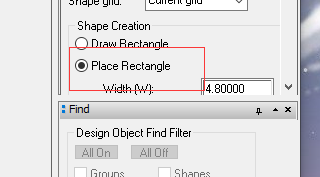

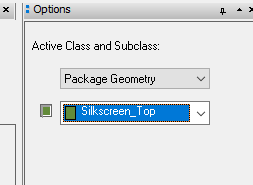

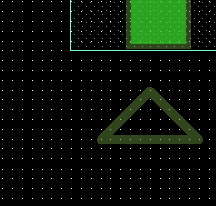

(3)绘制pcb封装库

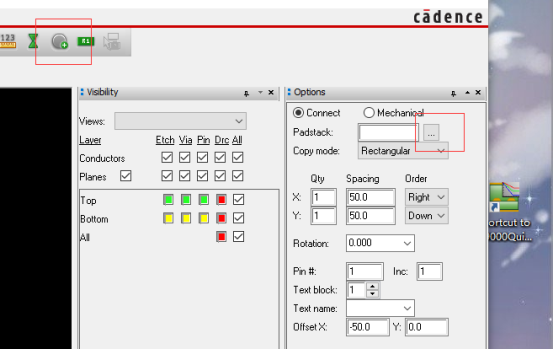

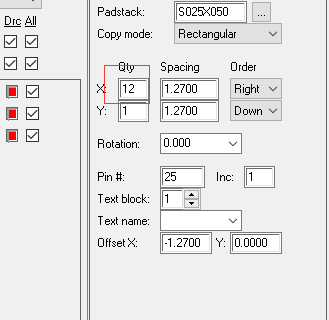

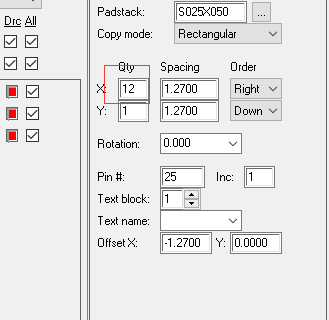

根据说明文档进行绘制  首先 打开pcb封装文件 然后 file new 选择package symbol 进行pcb焊盘库操作 修改对应的参数 将文件保存到对应的pcb封装库中

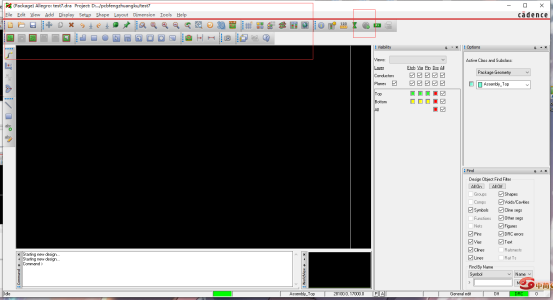

首先 打开pcb封装文件 然后 file new 选择package symbol 进行pcb焊盘库操作 修改对应的参数 将文件保存到对应的pcb封装库中  此时就可以进行焊盘的相关操作了

此时就可以进行焊盘的相关操作了  首先 要指定自己刚刚创建的焊盘库 路径 set up user

首先 要指定自己刚刚创建的焊盘库 路径 set up user

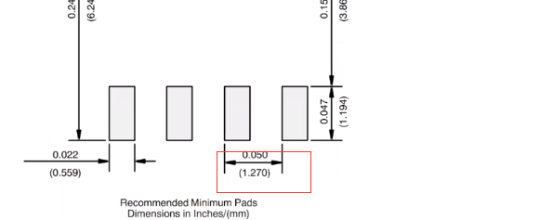

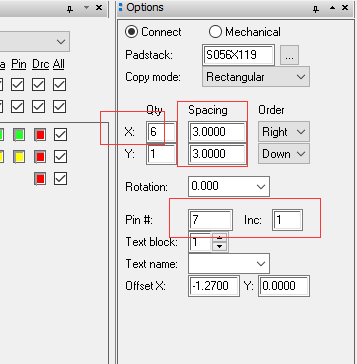

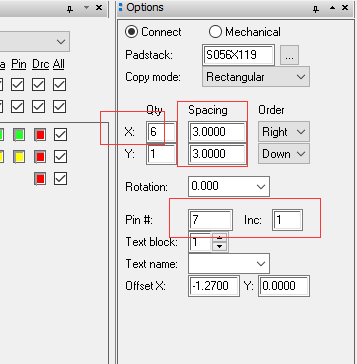

然后修改参数 格点 板子单位 毫米都在setup中修改 grids design 根据说明文档上进行设置1.27或者1.27的倍数 pin到pin之间的距离

然后修改参数 格点 板子单位 毫米都在setup中修改 grids design 根据说明文档上进行设置1.27或者1.27的倍数 pin到pin之间的距离  当我们设置1.27 发现 只有中心在焊盘上 则可以将格点给为1.27/2=0.635 就好了 都是在毫米单位下 操作的 修改参数 1.显示原点坐标 以及设置其位置合理 Setup 第一个 显示原点

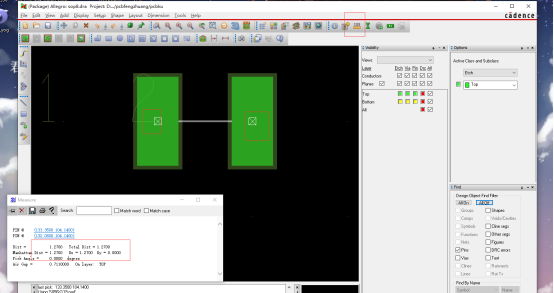

当我们设置1.27 发现 只有中心在焊盘上 则可以将格点给为1.27/2=0.635 就好了 都是在毫米单位下 操作的 修改参数 1.显示原点坐标 以及设置其位置合理 Setup 第一个 显示原点  若找不到 则 关闭格点 进行查看 然后将需要的焊盘 放置到原点附近位置 放置焊盘: 点击 圆形焊盘 然后右上角选择 对应的焊盘 进行相关的绘制 然后左键单机 即可

若找不到 则 关闭格点 进行查看 然后将需要的焊盘 放置到原点附近位置 放置焊盘: 点击 圆形焊盘 然后右上角选择 对应的焊盘 进行相关的绘制 然后左键单机 即可

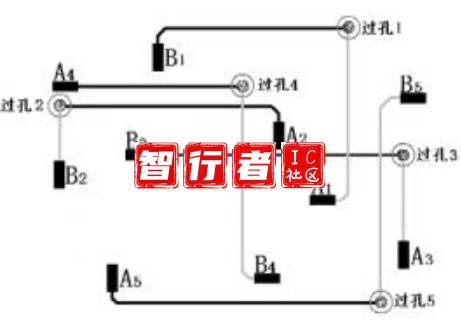

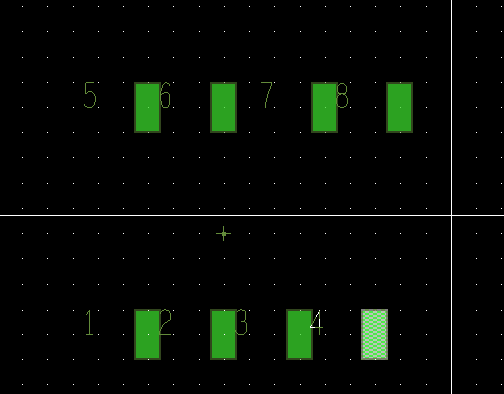

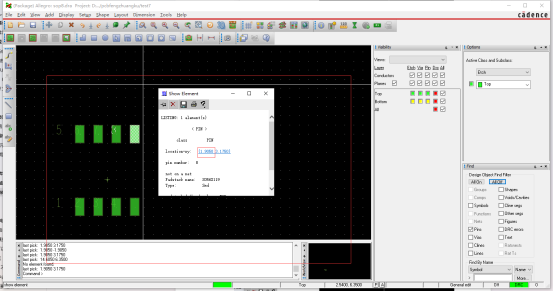

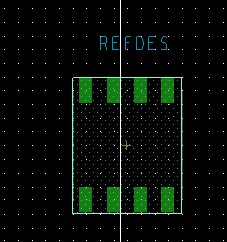

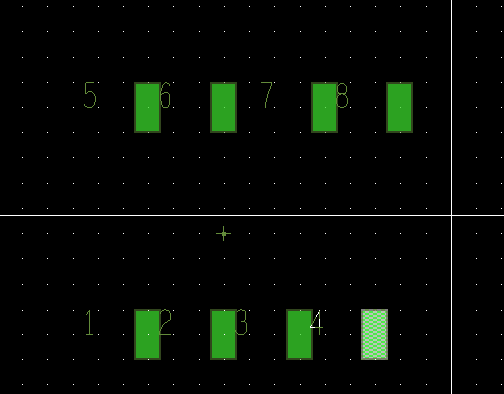

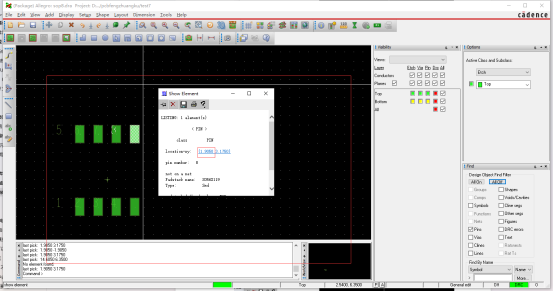

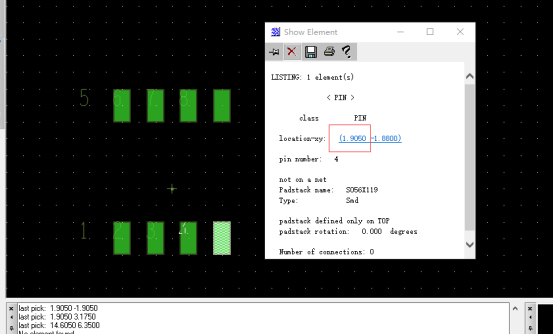

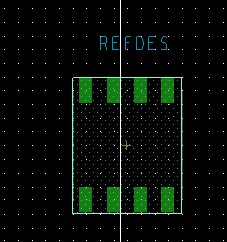

注意:焊盘的整体位置 要在坐标原点的中心 而且要保证上下一致 由于放置的是焊盘 即pin 故只需要查看当前焊盘的信息即可

注意:焊盘的整体位置 要在坐标原点的中心 而且要保证上下一致 由于放置的是焊盘 即pin 故只需要查看当前焊盘的信息即可  然后根据信息进行移动位置即可

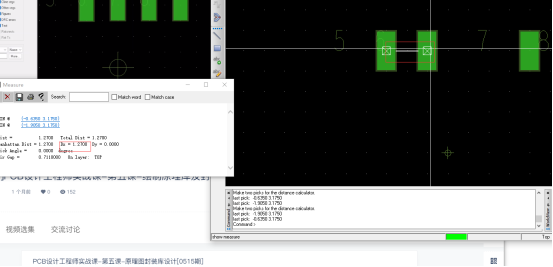

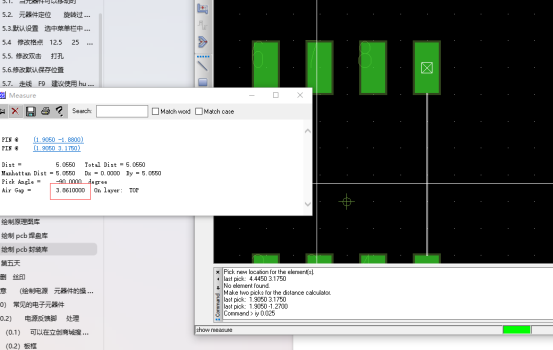

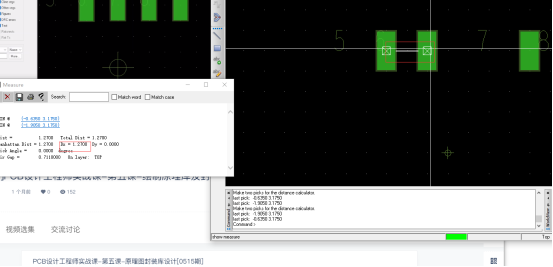

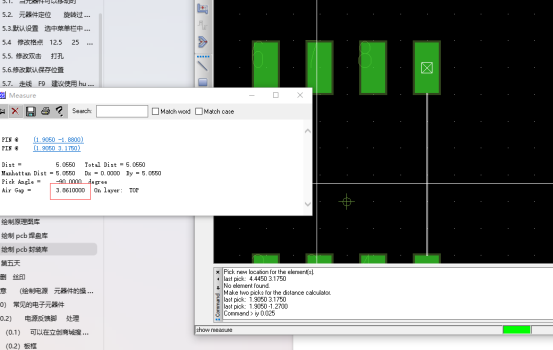

然后根据信息进行移动位置即可  移动位置: 使用距离工具 进行测量距离 pin之间的dx=1.27 调整y轴位置

移动位置: 使用距离工具 进行测量距离 pin之间的dx=1.27 调整y轴位置  3.886-3.861=0.025 因此需要下面一排上移0.025个单位

3.886-3.861=0.025 因此需要下面一排上移0.025个单位  先整体移动 然后 在控制台 iy 0.025 向上移动 Iy空格0.1 y轴向上移动0.1个单位

先整体移动 然后 在控制台 iy 0.025 向上移动 Iy空格0.1 y轴向上移动0.1个单位  此时 再测量距离

此时 再测量距离  然后调整x轴位置

然后调整x轴位置

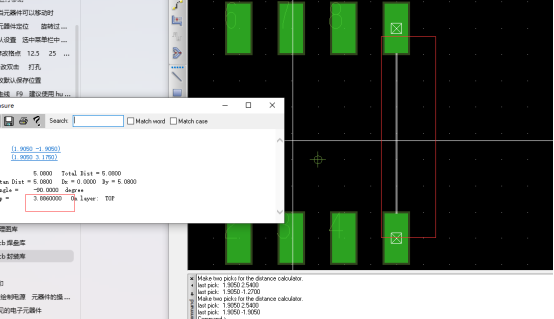

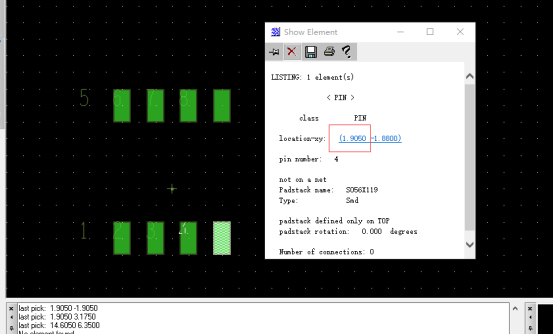

同理计算误差 选择移动 第二行1.9050第一行 1.9050 则此时不需要移动位置 Ix 0.705 ——-原点坐标是0 0 此时整体移动 x向右移动 1.27/2 =0.635个单位即可 Ix 0.635 即可对称

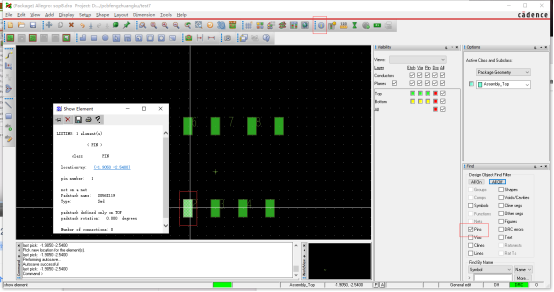

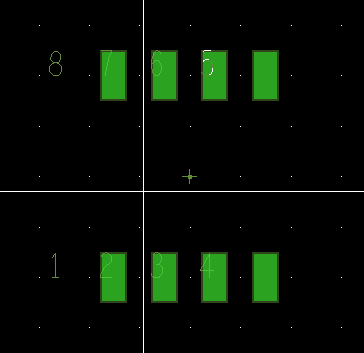

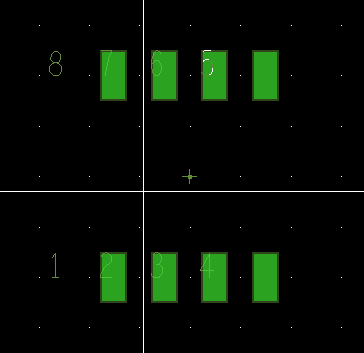

同理计算误差 选择移动 第二行1.9050第一行 1.9050 则此时不需要移动位置 Ix 0.705 ——-原点坐标是0 0 此时整体移动 x向右移动 1.27/2 =0.635个单位即可 Ix 0.635 即可对称  注意 pcb封装中的pin 脚必须要跟说明书上的保持一致 可以右键数字8 edit进行编辑

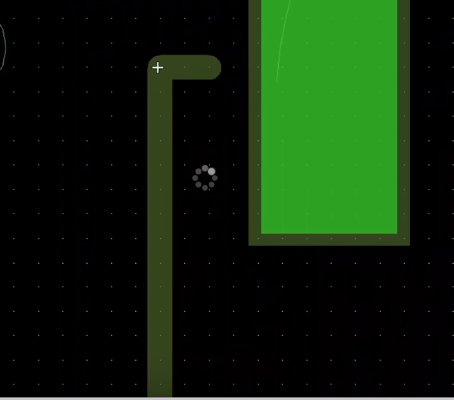

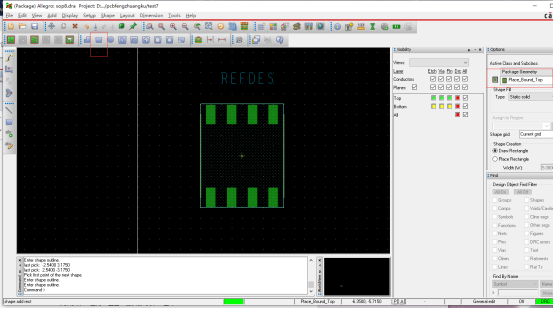

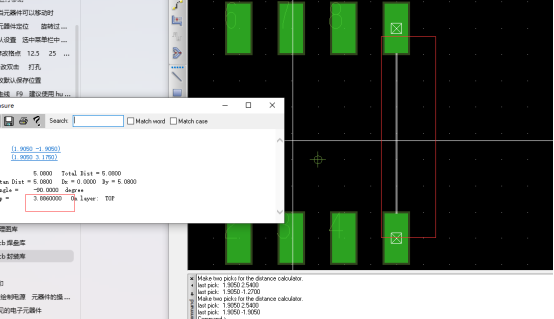

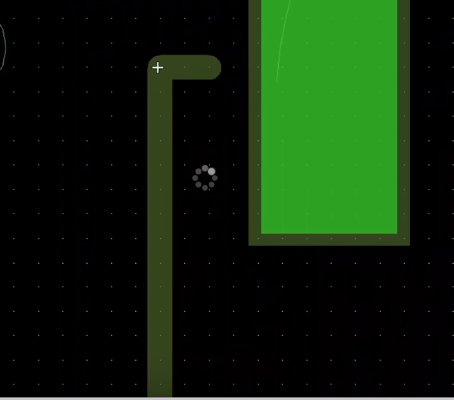

注意 pcb封装中的pin 脚必须要跟说明书上的保持一致 可以右键数字8 edit进行编辑  此时pin已经完成 然后添加丝印 规格书上的E

此时pin已经完成 然后添加丝印 规格书上的E

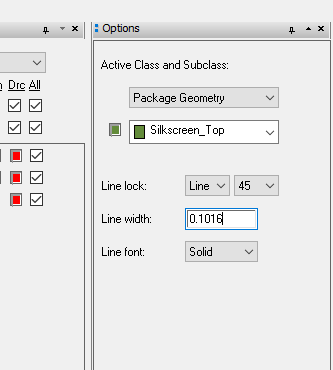

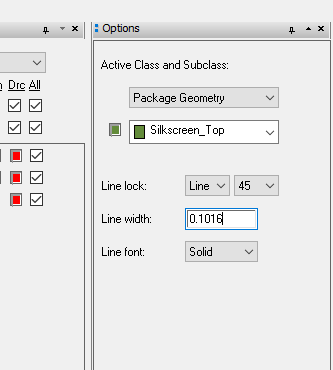

丝印 位置(放在能够快速定位的地方) 此时可以将格点改小一点 方便走线 装配层 铜皮

丝印 位置(放在能够快速定位的地方) 此时可以将格点改小一点 方便走线 装配层 铜皮

丝印框不需要很准确 要比实体大即可 不能画在焊盘上

丝印框不需要很准确 要比实体大即可 不能画在焊盘上  也可以带 横向

也可以带 横向  然后 直接 添加字符 写字 ref des

然后 直接 添加字符 写字 ref des

添加字体 refdes

添加字体 refdes  然后绘制装配层 铜皮 (将丝印也包裹住) 要将所有的管脚都包住

然后绘制装配层 铜皮 (将丝印也包裹住) 要将所有的管脚都包住

添加本体 实体 中间一部分

添加本体 实体 中间一部分  同理选择铜皮 选择对应的位置

同理选择铜皮 选择对应的位置  然后画在pin脚的位置上即可 有个大概即可

然后画在pin脚的位置上即可 有个大概即可  放置矩形

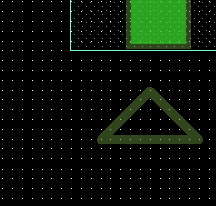

放置矩形  X 00即是原点坐标 在丝印层绘制1脚标识 1脚标识 三角 圆圈 箭头都可以 丝印 要在丝印外面

X 00即是原点坐标 在丝印层绘制1脚标识 1脚标识 三角 圆圈 箭头都可以 丝印 要在丝印外面

—–此时 就完成了pcb的封装库 快速放置 焊盘

—–此时 就完成了pcb的封装库 快速放置 焊盘

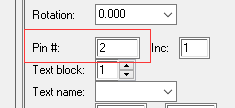

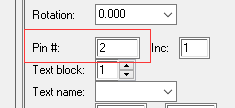

(2)通孔焊盘 修改焊盘编号

(2)通孔焊盘 修改焊盘编号  通孔 1

通孔 1  圆形焊盘 因为不是镶嵌进去的 故不需要勾选single

圆形焊盘 因为不是镶嵌进去的 故不需要勾选single  显示 焊盘通孔

显示 焊盘通孔  [/ceo-payment-hide]

[/ceo-payment-hide]

然后修改页面大小 在菜单栏的options中 选择schematic page 【a最小】 –双击放置器件 右键 End modle取消 –框选器件 然后可以移动 –GND 地线

然后修改页面大小 在菜单栏的options中 选择schematic page 【a最小】 –双击放置器件 右键 End modle取消 –框选器件 然后可以移动 –GND 地线  –VCC5电源 –连线

–VCC5电源 –连线  快捷建 W esc直接取消连线操作 –没有连上的线 则表示该引脚未使用 –写字 标注 然后移动到对应的位置上 快捷建 N (只能放在自己画的黑线上)

快捷建 W esc直接取消连线操作 –没有连上的线 则表示该引脚未使用 –写字 标注 然后移动到对应的位置上 快捷建 N (只能放在自己画的黑线上)  –显示 GND 双击GND图标 然后修改默认显示 保存关闭即可

–显示 GND 双击GND图标 然后修改默认显示 保存关闭即可  –显示晶振的默认值 双击 晶振元器件

–显示晶振的默认值 双击 晶振元器件  若未显示 则右键 当前晶振数值 display 选择Value only 保存即可

若未显示 则右键 当前晶振数值 display 选择Value only 保存即可  –修改格点

–修改格点  –然后选择对应的组件 电阻RES_0 — 当原理图完成后 然后进行 导出网表 操作 –注意 判断是否连接上 可以将先拖动一下 若一起移动则连接成功

–然后选择对应的组件 电阻RES_0 — 当原理图完成后 然后进行 导出网表 操作 –注意 判断是否连接上 可以将先拖动一下 若一起移动则连接成功 然后 选中当前的pcb原理图库文件 右键 new part

然后 选中当前的pcb原理图库文件 右键 new part  名字 U类型 下面两个 左边是分割

名字 U类型 下面两个 左边是分割  注意一定要给元器件 留有足够的空间 不然会叠在一起 一般绘制过程 —-不需要考虑绘制的pcb原理图有多大 第一个 画pin脚标识 第二个和第三个 是用来 改变封装大小的 第四个 快速添加序号用的

注意一定要给元器件 留有足够的空间 不然会叠在一起 一般绘制过程 —-不需要考虑绘制的pcb原理图有多大 第一个 画pin脚标识 第二个和第三个 是用来 改变封装大小的 第四个 快速添加序号用的  当画成矩形的时候 直接可以移动大小

当画成矩形的时候 直接可以移动大小  Pcb原理图 双击空白处 即是元器件 修改属性为false 电阻 顶层

Pcb原理图 双击空白处 即是元器件 修改属性为false 电阻 顶层  管脚很多 使用矩阵放置 选中多个引脚 右键 第一个 修改

管脚很多 使用矩阵放置 选中多个引脚 右键 第一个 修改  右键 库文件 add 选择 官放原理图 方库文件 【一般情况 直接使用公司的库文件】 右键别人的库里面的某个封装 copy 然后 选择自己的库路径 右键 paste

右键 库文件 add 选择 官放原理图 方库文件 【一般情况 直接使用公司的库文件】 右键别人的库里面的某个封装 copy 然后 选择自己的库路径 右键 paste

PLACE 连页符 off page 磁珠(类似于电阻) bead 当我们二次修改 pcb原理图时 就可以在design中右键 要更新的元器件 update一下 CAP 电源

PLACE 连页符 off page 磁珠(类似于电阻) bead 当我们二次修改 pcb原理图时 就可以在design中右键 要更新的元器件 update一下 CAP 电源  当我们绘制pcb的原理图时 desige Cache中才会显示内容

当我们绘制pcb的原理图时 desige Cache中才会显示内容

使用快速添加pin脚

使用快速添加pin脚  右键框选 然后编辑

右键框选 然后编辑  Pcb的封装 必须严格要求 红色的 焊盘(PAD) 丝印框(silk) 专门画 焊盘 Pad_Designer 贴片 0 plated电镀 内壁普通 本体层 装配层 比器件 大一点 透视图 用虚线表示 D X E 钢网 焊盘库 长方形 (长* 宽) 汉字 REF DES

Pcb的封装 必须严格要求 红色的 焊盘(PAD) 丝印框(silk) 专门画 焊盘 Pad_Designer 贴片 0 plated电镀 内壁普通 本体层 装配层 比器件 大一点 透视图 用虚线表示 D X E 钢网 焊盘库 长方形 (长* 宽) 汉字 REF DES  1.焊盘的相关操作 先使用pad工具 绘制焊盘 修改单位为毫米

1.焊盘的相关操作 先使用pad工具 绘制焊盘 修改单位为毫米  参数:hole type 孔的类型 表贴焊盘 通孔焊盘 贴片的不用修改 single只有单层 不勾选则是含有多层 然后进行绘制焊盘的先关操作: 辨别是否是表贴器件还是通孔器件 看管脚是直的还是竖直的

参数:hole type 孔的类型 表贴焊盘 通孔焊盘 贴片的不用修改 single只有单层 不勾选则是含有多层 然后进行绘制焊盘的先关操作: 辨别是否是表贴器件还是通孔器件 看管脚是直的还是竖直的

一般没有推荐尺寸时 使用最大值进行绘制pcb焊盘

一般没有推荐尺寸时 使用最大值进行绘制pcb焊盘

推荐的 可以在下面看到 括号中的是毫米单位

推荐的 可以在下面看到 括号中的是毫米单位  由此可见 宽 0.559 长1.194 然后 pad进行绘制 右上角 选择top 顶视图 x是横切面 Rect 矩形 可以拖动小方块 使其全展开

由此可见 宽 0.559 长1.194 然后 pad进行绘制 右上角 选择top 顶视图 x是横切面 Rect 矩形 可以拖动小方块 使其全展开

当创建完成后file save as 进行保存 命名规范

当创建完成后file save as 进行保存 命名规范  原来的尺寸是 0.559X1.1940 s是表贴矩形焊盘 使用四舍五入 取056就相当于0.56毫米 119=1.19 此时pcb焊盘做完以后 就可以进行绘制pcb封装库了

原来的尺寸是 0.559X1.1940 s是表贴矩形焊盘 使用四舍五入 取056就相当于0.56毫米 119=1.19 此时pcb焊盘做完以后 就可以进行绘制pcb封装库了 此时就可以进行焊盘的相关操作了

此时就可以进行焊盘的相关操作了  首先 要指定自己刚刚创建的焊盘库 路径 set up user

首先 要指定自己刚刚创建的焊盘库 路径 set up user

然后修改参数 格点 板子单位 毫米都在setup中修改 grids design 根据说明文档上进行设置1.27或者1.27的倍数 pin到pin之间的距离

然后修改参数 格点 板子单位 毫米都在setup中修改 grids design 根据说明文档上进行设置1.27或者1.27的倍数 pin到pin之间的距离  当我们设置1.27 发现 只有中心在焊盘上 则可以将格点给为1.27/2=0.635 就好了 都是在毫米单位下 操作的 修改参数 1.显示原点坐标 以及设置其位置合理 Setup 第一个 显示原点

当我们设置1.27 发现 只有中心在焊盘上 则可以将格点给为1.27/2=0.635 就好了 都是在毫米单位下 操作的 修改参数 1.显示原点坐标 以及设置其位置合理 Setup 第一个 显示原点  若找不到 则 关闭格点 进行查看 然后将需要的焊盘 放置到原点附近位置 放置焊盘: 点击 圆形焊盘 然后右上角选择 对应的焊盘 进行相关的绘制 然后左键单机 即可

若找不到 则 关闭格点 进行查看 然后将需要的焊盘 放置到原点附近位置 放置焊盘: 点击 圆形焊盘 然后右上角选择 对应的焊盘 进行相关的绘制 然后左键单机 即可

注意:焊盘的整体位置 要在坐标原点的中心 而且要保证上下一致 由于放置的是焊盘 即pin 故只需要查看当前焊盘的信息即可

注意:焊盘的整体位置 要在坐标原点的中心 而且要保证上下一致 由于放置的是焊盘 即pin 故只需要查看当前焊盘的信息即可  然后根据信息进行移动位置即可

然后根据信息进行移动位置即可  3.886-3.861=0.025 因此需要下面一排上移0.025个单位

3.886-3.861=0.025 因此需要下面一排上移0.025个单位  先整体移动 然后 在控制台 iy 0.025 向上移动 Iy空格0.1 y轴向上移动0.1个单位

先整体移动 然后 在控制台 iy 0.025 向上移动 Iy空格0.1 y轴向上移动0.1个单位  此时 再测量距离

此时 再测量距离  然后调整x轴位置

然后调整x轴位置

同理计算误差 选择移动 第二行1.9050第一行 1.9050 则此时不需要移动位置 Ix 0.705 ——-原点坐标是0 0 此时整体移动 x向右移动 1.27/2 =0.635个单位即可 Ix 0.635 即可对称

同理计算误差 选择移动 第二行1.9050第一行 1.9050 则此时不需要移动位置 Ix 0.705 ——-原点坐标是0 0 此时整体移动 x向右移动 1.27/2 =0.635个单位即可 Ix 0.635 即可对称  注意 pcb封装中的pin 脚必须要跟说明书上的保持一致 可以右键数字8 edit进行编辑

注意 pcb封装中的pin 脚必须要跟说明书上的保持一致 可以右键数字8 edit进行编辑  此时pin已经完成 然后添加丝印 规格书上的E

此时pin已经完成 然后添加丝印 规格书上的E

丝印 位置(放在能够快速定位的地方) 此时可以将格点改小一点 方便走线 装配层 铜皮

丝印 位置(放在能够快速定位的地方) 此时可以将格点改小一点 方便走线 装配层 铜皮

丝印框不需要很准确 要比实体大即可 不能画在焊盘上

丝印框不需要很准确 要比实体大即可 不能画在焊盘上  也可以带 横向

也可以带 横向  然后 直接 添加字符 写字 ref des

然后 直接 添加字符 写字 ref des

添加字体 refdes

添加字体 refdes  然后绘制装配层 铜皮 (将丝印也包裹住) 要将所有的管脚都包住

然后绘制装配层 铜皮 (将丝印也包裹住) 要将所有的管脚都包住

添加本体 实体 中间一部分

添加本体 实体 中间一部分  同理选择铜皮 选择对应的位置

同理选择铜皮 选择对应的位置  然后画在pin脚的位置上即可 有个大概即可

然后画在pin脚的位置上即可 有个大概即可  放置矩形

放置矩形  X 00即是原点坐标 在丝印层绘制1脚标识 1脚标识 三角 圆圈 箭头都可以 丝印 要在丝印外面

X 00即是原点坐标 在丝印层绘制1脚标识 1脚标识 三角 圆圈 箭头都可以 丝印 要在丝印外面

—–此时 就完成了pcb的封装库 快速放置 焊盘

—–此时 就完成了pcb的封装库 快速放置 焊盘

(2)通孔焊盘 修改焊盘编号

(2)通孔焊盘 修改焊盘编号  通孔 1

通孔 1  圆形焊盘 因为不是镶嵌进去的 故不需要勾选single

圆形焊盘 因为不是镶嵌进去的 故不需要勾选single  显示 焊盘通孔

显示 焊盘通孔  [/ceo-payment-hide]

[/ceo-payment-hide]